## REALIZATION AND ANALYSIS OF HIGH PERFORMANCE PHYSICAL UNCLONABLE FUNCTIONS BASED ON RING OSCILLATORS

by

Giray Kömürcü

B.S., Microelectronics Engineering, Sabanci University, 2005M.S., Electrical & Electronics Engineering, Boğaziçi University, 2008

Submitted to the Institute for Graduate Studies in Science and Engineering in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Graduate Program in Electrical and Electronics Engineering Boğaziçi University

2014

# REALIZATION AND ANALYSIS OF HIGH PERFORMANCE PHYSICAL UNCLONABLE FUNCTIONS BASED ON RING OSCILLATORS

### APPROVED BY:

| Prof. Günhan Dündar                   |  |

|---------------------------------------|--|

| (Thesis Supervisor)                   |  |

|                                       |  |

| Assist. Prof. Ali Emre Pusane         |  |

| (Thesis Co-supervisor)                |  |

|                                       |  |

| Assoc. Prof. Sıddıka Berna Örs Yalçın |  |

|                                       |  |

| Assoc. Prof. Arda Yurdakul            |  |

|                                       |  |

| Assist. Prof. İsmail Faik Başkaya     |  |

DATE OF APPROVAL: 29.05.2014

### ACKNOWLEDGEMENTS

I would like to express my deep gratitude to my thesis supervisor, Prof. Günhan Dündar for giving me the pleasure of being his student during my M.Sc. and PhD studies. He has involved very closely to my thesis and given very valuable ideas. His vast knowledge, continuous support, and perfect guidance lead my research to a successful conclusion.

I am also very grateful to my co-advisor Assist. Prof. Ali Emre Pusane for being my supervisor during the PhD studies. His deep knowledge and point of view helped significantly to develop, bring to perfection, and conclude my thesis in every aspect. I felt his positive manner, energy, and very valuable support during the entire period of my PhD studies.

I would also like to thank Assoc. Prof. Arda Yurdakul, Assist. Prof. I. Faik Başkaya, and Assoc. Prof. S. Berna Örs Yalçın for being a part of my thesis committee. Their ideas and advises definetely improved the quality of this thesis.

I would also like to express my gratitude to Dr. Aziz Ulvi Çalışkan who has been a lot more than an employer to me in the last decade. I have felt his support, encouragement, and positive manner during my academic and work life. Everything would be much harder without his continuous support.

My special thanks goes to Dr. Yaman Özelçi who has supported my M.Sc. and PhD studies with great patience and tolerance. I have learnt a lot from his knowledge and engineering skills. He has also helped on the most important step of this PhD study by proposing the topic of the thesis, which has eased my work significantly.

I owe really much to my colleagues and friends Sedat Soydan, Umut Güvenç, and Ülkühan Güler, who have helped creating a very friendly and cheerful working environment in the past nine years. They have also contributed to my PhD studies with their remarkable ideas, assistances, and support.

I would like to state my sincere gratitude to my mom Hülya Kömürcü, who has taught the importance of education since the first day of primary school and helped me in every aspect for my success without showing a sign of tiredness at any time. I would not find the power to continue my academic life without her passionate support.

Finally, I would like to express my deepest gratitude and my love to my wife, Elif Sezgin Kömürcü and my daughter, Neva for their love, patience, understanding, and all the sacrifices they made during my thesis study. It would be impossible to complete this thesis without them. Their existence is the most meaningful thing in my life.

Above all, I dedicate this thesis to the memory of my beloved father, Feyzi Kömürcü, who has unfortunately passed away during my PhD studies. He has spent his whole life for the sake of his family and supported our education passionately. I owe my existence and success in my life to him.

### ABSTRACT

# REALIZATION AND ANALYSIS OF HIGH PERFORMANCE PHYSICAL UNCLONABLE FUNCTIONS BASED ON RING OSCILLATORS

Physical Unclonable Functions (PUFs) are powerful techniques that are proposed recently to address security related problems. They have a wide range of applications including cryptographic key generation and storage, authentication, identity generation, and intellectual property protection. PUFs offer new, low cost, and secure solutions in these areas with their ability to generate chip specific signatures on the fly. In the scope of the thesis study, quality metrics for the robustness and uniqueness properties of PUF circuits are derived. Confidence interval and confidence level concepts are adapted to PUF performance evaluation for the reliability of the results. Theoretical background of Ring Oscillators (ROs) is studied to analyze the effect of the number of stages and measurement time in RO-PUFs. Depending on the theoretical calculations, optimum number of stages and measurement time are determined and the theory is validated via experimental analysis. Then, ordering based RO-PUFs, which aim to maximize the robustness and entropy extraction, are discussed and dynamic programming is adapted for achieving lower complexity in the grouping step. Next, systematic analysis of the bit error probability in ordering based RO-PUFs is performed and area usage vs. robustness tradeoff is presented. Implementation and analysis of error correction codes to maintain the robustness in ordering based RO-PUFs are also discussed. In addition to these, two challenge-response pair enhancement methods for ordering based RO-PUFs are introduced. Finally, effects of aging on ordering based RO-PUFs and compensation mechanisms are presented.

### ÖZET

# HALKA OSİLATÖRÜ TABANLI VE YÜKSEK PERFORMANSLI FİZİKSEL KLONLANAMAZ FONKSİYON ANALİZİ VE GERÇEKLENMESİ

Fiziksel Klonlanamaz Fonksiyonlar (PUF) güvenlik uygulamalarında kullanılmak üzere tasarlanan güçlü tekniklerdir. Kullanım alanları arasında kriptografik anahtar üretimi ve depolaması, doğrulama, kimlik üretme ve fikri mülkiyet korunumu gibi uvgulamalar bulunmaktadır. PUF'lar çalışma esnasında entegre devreye özgü imza üretme kabiliyetleriyle yeni, düşük maliyetli ve yüksek güvenlikli çözümler sunmaktadırlar. Tez çalışması kapsamında, PUF çıktılarının sağlamlık ve özgünlüklerini belirleyebilemek için kalite ölçütleri belirlenmiştir. Güven aralığı ve güven seviyesi kavramları PUF değerlendirme sürecine entegre edilerek sonucların güvenilirliğinin sağlanması hedeflenmiştir. Halka osilatörlerin (RO) kuramsal temelleri çalışılarak, RO-PUF'lar için katman sayısı ve ölçüm zamanını en iyileme yöntemleri araştırılmıştır. Bu konuda kuramsal olarak belirlenen yöntemler deneysel verilerle de doğrulanmıştır. Sonrasında, RO-PUF çıktılarının sağlamlığını ve entropi kullanımını arttırmak için önerilen sıralama tabanlı RO-PUF sunulmuş, Dinamik Programlama gruplama adımına entegre edilerek algoritma karmaşıklığının azalması sağlanmıştır. Bunların yanında, sıralama tabanlı RO-PUF'larda hata analizi yapılmış ve alan kullanımı ile sağlamlık ilişkisi incelenmiştir. Olası hatalı çıktıları düzeltmek için hata düzeltme kodları uygulanmış ve analiz edilmiştir. Bunların yanında, sıralama tabanlı RO-PUF'lara yönelik iki adet sorgu-cevap çifti üretme metodu geliştirilmiş ve bu yöntemlerin güvenli bir şekilde kullanılabilmesi için üç adet güvenli kullanım senaryosu sunulmuştur. Son olarak, yaşlanmanın sıralama tabanlı RO-PUF'lar üzerindeki etkileri incelenmiş ve bu yaşlanma etkilerini düzeltme teknikleri geliştirilmiştir.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                  |

|---------------------------------------------------|

| ABSTRACT                                          |

| ÖZETv                                             |

| LIST OF FIGURES                                   |

| LIST OF TABLES                                    |

| LIST OF SYMBOLS                                   |

| LIST OF ACRONYMS/ABBREVIATIONS                    |

| 1. INTRODUCTION                                   |

| 1.1. Motivation                                   |

| 1.2. Contributions and Organization of the Thesis |

| 2. PHYSICAL UNCLONABLE FUNCTIONS                  |

| 2.1. Definition and Applications                  |

| 2.2. PUF Properties                               |

| 2.2.1. Uniqueness                                 |

| 2.2.2. Robustness                                 |

| 2.2.3. Unclonability $\ldots$                     |

| 2.2.4. Unpredictability                           |

| 2.3. PUF Types                                    |

| 2.3.1. Optical PUF                                |

| 2.3.2. Coating PUF                                |

| 2.3.3. Arbiter PUF                                |

| 2.3.4. Glitch PUF $\ldots$ $1^4$                  |

| 2.3.5. Memory Based PUF                           |

| 2.3.5.1. SRAM PUF                                 |

| 2.3.5.2. Butterfly PUF                            |

| 2.3.6. RST PUF                                    |

| 2.3.7. Ring Oscillator PUF                        |

| 3. DERIVATION OF QUALITY METRICS                  |

|    | 3.1. | Derivation of Quality Metrics for Uniqueness                                       | 25  |

|----|------|------------------------------------------------------------------------------------|-----|

|    | 3.2. | Derivation of Quality Metrics for Robustness                                       | 28  |

|    | 3.3. | Confidence Interval and Confidence Level Concepts for PUF Evaluation               | 31  |

|    | 3.4. | Implementation of Two Basic RO-PUF Structures                                      | 32  |

|    | 3.5. | Analysis of Experimental Data                                                      | 33  |

| 4. | OPT  | ΓΙΜΙΖΙΝG RO-PUF CIRCUITS                                                           | 37  |

|    | 4.1. | Effect of the Number of Stages                                                     | 38  |

|    | 4.2. | Effect of the Measurement Time                                                     | 41  |

|    | 4.3. | Experimental Analysis and Validation of the Theory                                 | 43  |

| 5. | ORI  | DERING BASED RO-PUF CIRCUITS                                                       | 48  |

|    | 5.1. | Maximizing Robustness and Entropy in RO-PUF Circuits                               | 48  |

|    | 5.2. | Adapting Dynamic Programming to RO-PUFs                                            | 53  |

|    |      | 5.2.1. Proof of Lower Complexity of DP Method over LISA by Con-                    |     |

|    |      | tradiction                                                                         | 56  |

|    | 5.3. | Experimental Analysis and Validation of the Theory                                 | 59  |

| 6. | ERF  | ROR PROBABILITY IN ORDERING BASED RO-PUFs AND ANALYSIS                             |     |

|    | OF   | ERROR CORRECTION CODES                                                             | 69  |

|    | 6.1. | Systematic Analysis of Bit Error Probability                                       | 69  |

|    |      | 6.1.1. Group Length Analysis                                                       | 70  |

|    |      | 6.1.2. Symbol Error Probability and Validation                                     | 71  |

|    |      | 6.1.3. Symbol Error to Bit Error Conversion and Bit Error Probability              | 75  |

|    |      | 6.1.4. Worst Case Bit Errors per Problematic RO Pair                               | 77  |

|    | 6.2. | Area Usage vs. Robustness in Ordering Based RO-PUFs                                | 79  |

|    | 6.3. | Implementation and Analysis of Error Correction Codes                              | 83  |

| 7. | CRF  | P GENERATION                                                                       | 92  |

|    | 7.1. | CRP Concept in PUFs                                                                | 92  |

|    |      | 7.1.1. CRP Properties                                                              | 93  |

|    |      | 7.1.2. Importance of Large Number of CRPs                                          | 93  |

|    | 7.2. | Enhanced CRP Set with the $f_{thp}$ Selection Method $\ldots \ldots \ldots \ldots$ | 94  |

|    | 7.3. | Enhanced CRP Set with RO Selection Method                                          | 98  |

|    | 7.4. | Comparison of the $f_{thp}$ Selection and RO Selection Methods 1                   | 103 |

| 8. | EFF  | ECTS OF AGING AND COMPENSATION MECHANISMS 1                       | 108 |

|----|------|-------------------------------------------------------------------|-----|

|    | 8.1. | Aging Mechanisms and PUFs                                         | 108 |

|    | 8.2. | Ordering Based RO-PUFs and Aging                                  | 10  |

|    | 8.3. | Accelerated Aging Test and Analysis of Results                    | 11  |

|    | 8.4. | Effects of Aging on Ordering Based RO-PUFs and Compensation Mech- |     |

|    |      | anisms                                                            | 16  |

| 9. | CON  | NCLUSION                                                          | 121 |

| AF | PEN  | IDIX A: LIST OF PUBLICATIONS                                      | 124 |

| RE | FER  | ENCES                                                             | 126 |

## LIST OF FIGURES

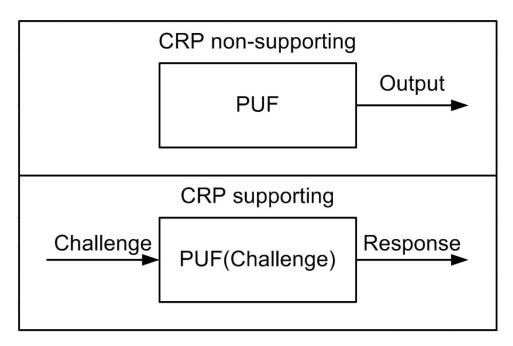

| Figure 2.1.  | CRP supporting and non supporting PUFs                               | 5  |

|--------------|----------------------------------------------------------------------|----|

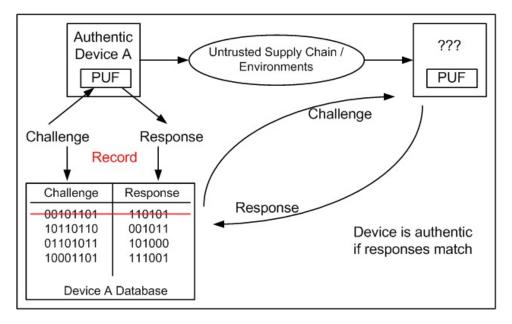

| Figure 2.2.  | PUF based authentication [1]                                         | 6  |

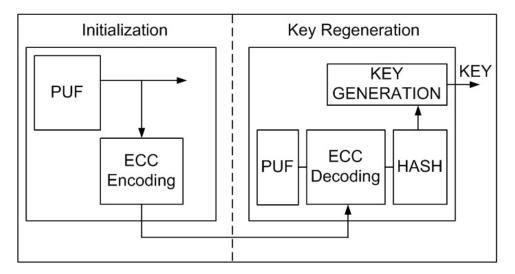

| Figure 2.3.  | Cryptographic key generation with PUFs [1]                           | 7  |

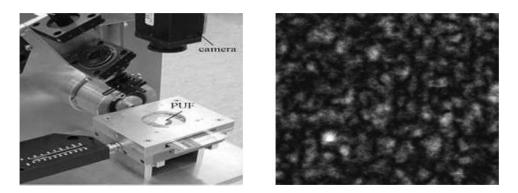

| Figure 2.4.  | Optical PUF measurement setup and pattern from a silicon surface [2] | 10 |

| Figure 2.5.  | Schematic cross-section of a coating PUF [3]                         | 11 |

| Figure 2.6.  | Arbiter based PUF circuit                                            | 12 |

| Figure 2.7.  | Feed-forward arbiter based PUF                                       | 12 |

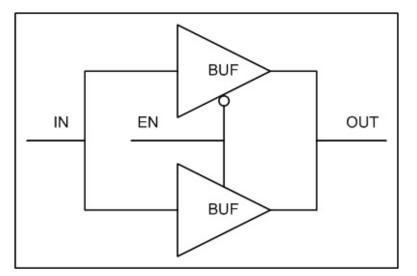

| Figure 2.8.  | Tristate buffer and truth table                                      | 13 |

| Figure 2.9.  | Delay unit in tristate buffers                                       | 13 |

| Figure 2.10. | PUF architecture built with tristate buffers                         | 14 |

| Figure 2.11. | Input network [4]                                                    | 15 |

| Figure 2.12. | Output network [4]                                                   | 15 |

| Figure 2.13. | BPUF operation [5]                                                   | 18 |

| Figure 2.14. | LUT based RST-PUF circuit [6]                                        | 19 |

| Figure 2.15. | RST PUF output generation [6]                                                                              | 20 |

|--------------|------------------------------------------------------------------------------------------------------------|----|

| Figure 2.16. | 5-stage RO schematic with enable input.                                                                    | 20 |

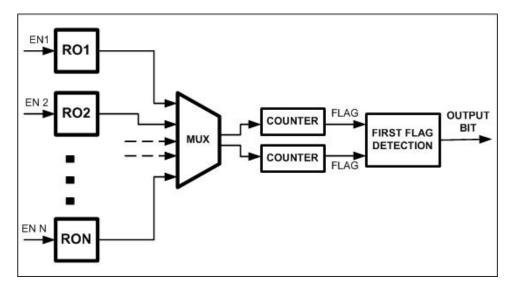

| Figure 2.17. | PUF output bit generation by conventional systems                                                          | 21 |

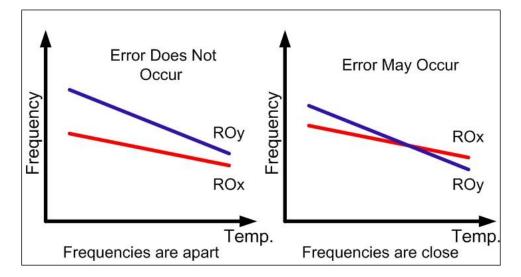

| Figure 2.18. | Effect of temperature variations on RO-PUF                                                                 | 21 |

| Figure 2.19. | Configurable RO-PUF scheme [7]                                                                             | 22 |

| Figure 2.20. | Location of ROs used for 1 bit generation.                                                                 | 24 |

| Figure 2.21. | Output generation mechanism proposed in [8]                                                                | 24 |

| Figure 3.1.  | Number of measurements - confidence level relation with confi-<br>dence interval of 0.01 and STD of 0.064. | 32 |

| Figure 3.2.  | Number of measurements - confidence level relation with confidence interval of 0.001 and STD of 0.064.     | 33 |

| Figure 4.1.  | 5-stage RO schematic with delay components mentioned                                                       | 39 |

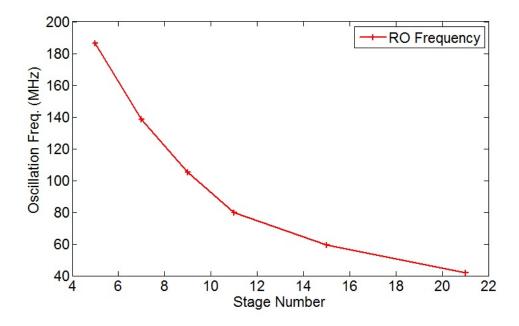

| Figure 4.2.  | Frequency of ROs vs. Stage Number.                                                                         | 44 |

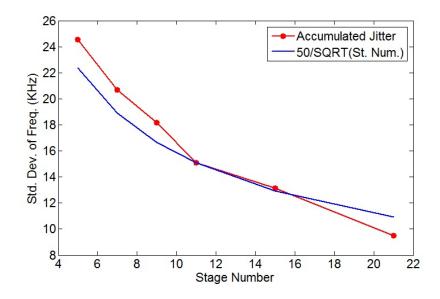

| Figure 4.3.  | Accumulated Jitter vs. Stage Number.                                                                       | 45 |

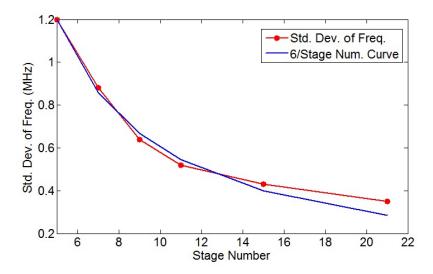

| Figure 4.4.  | Spatial Variation vs. Stage Number                                                                         | 45 |

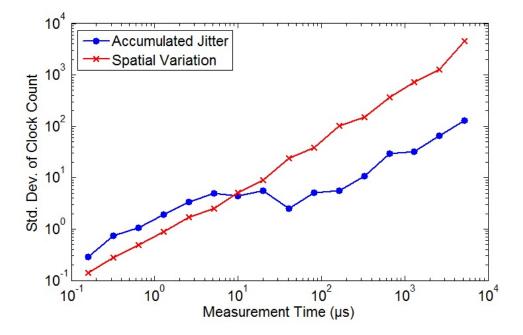

| Figure 4.5.  | Accumulated Jitter and Spatial Variation.                                                                  | 46 |

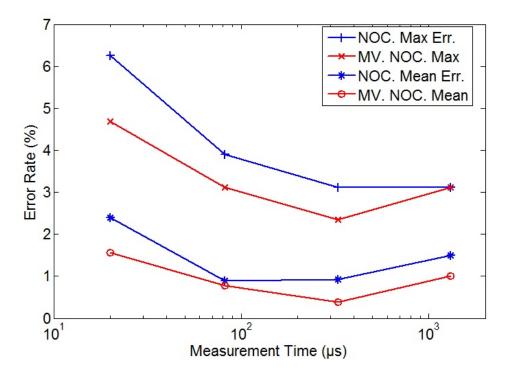

| Figure 4.6.  | Error Rate vs. Meas. Time for RO-PUF structure                                                             | 46 |

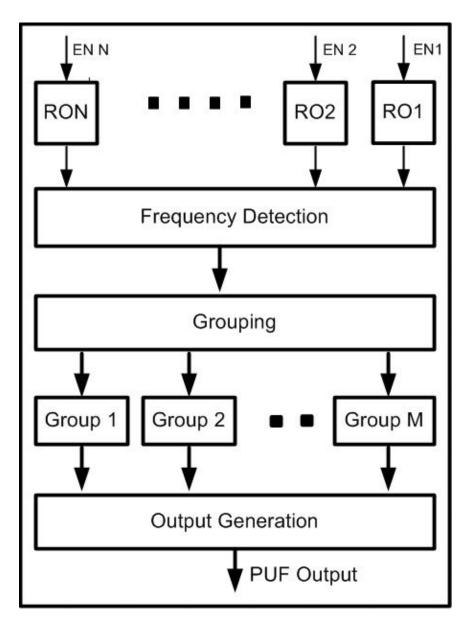

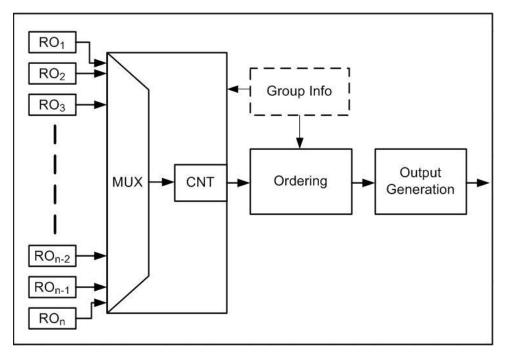

| Figure 5.1.  | PUF output generation by ordering based systems                               | 50 |

|--------------|-------------------------------------------------------------------------------|----|

| Figure 5.2.  | LISA in pseudo code [9]. $\ldots$ . $\ldots$ . $\ldots$ . $\ldots$ . $\ldots$ | 51 |

| Figure 5.3.  | Determining $f_{thp}$ in pseudo code                                          | 52 |

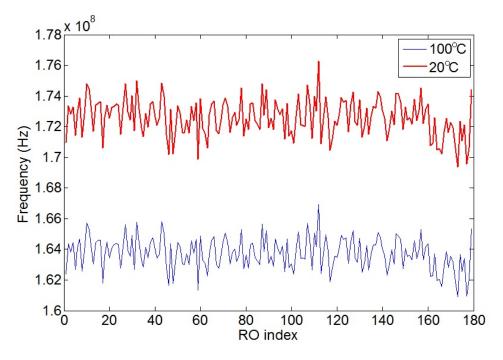

| Figure 5.4.  | Frequency of ROs measured at 20°C and 100°C                                   | 53 |

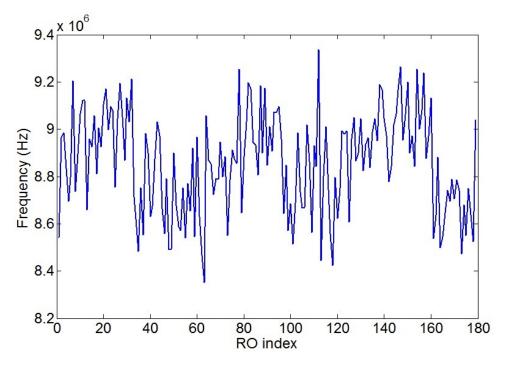

| Figure 5.5.  | Frequency deviation of ROs                                                    | 54 |

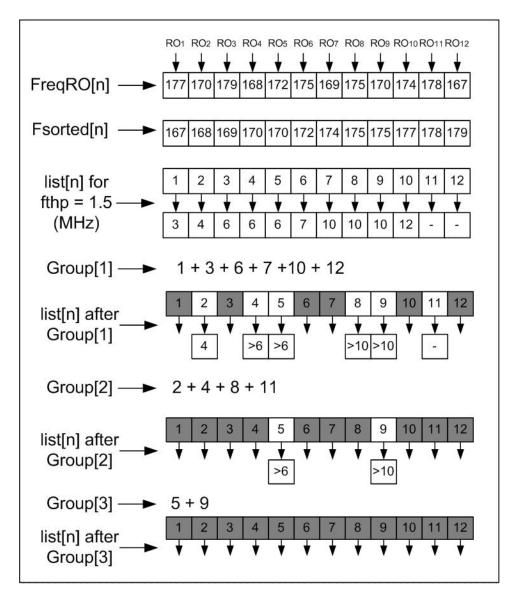

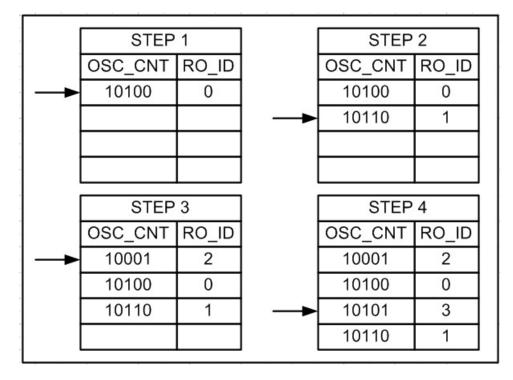

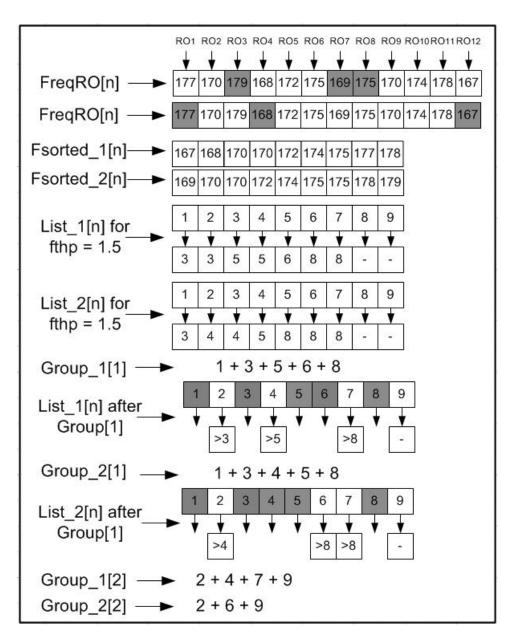

| Figure 5.6.  | DP sample execution for 12 elements                                           | 56 |

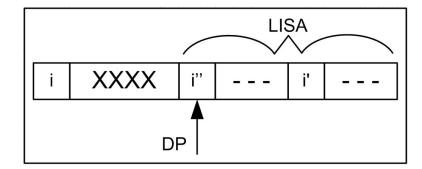

| Figure 5.7.  | Dynamic Programming in pseudo code                                            | 57 |

| Figure 5.8.  | Search for the largest group                                                  | 58 |

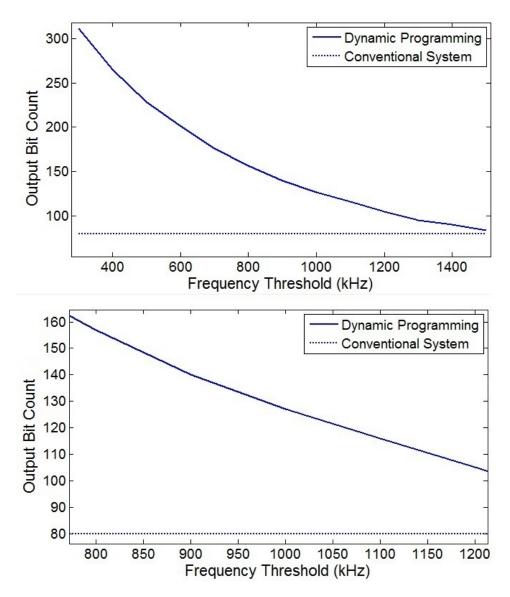

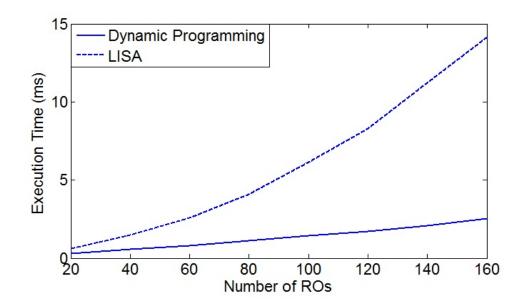

| Figure 5.9.  | PUF output bit generation comparison                                          | 61 |

| Figure 5.10. | Execution time of algorithms in Matlab.                                       | 62 |

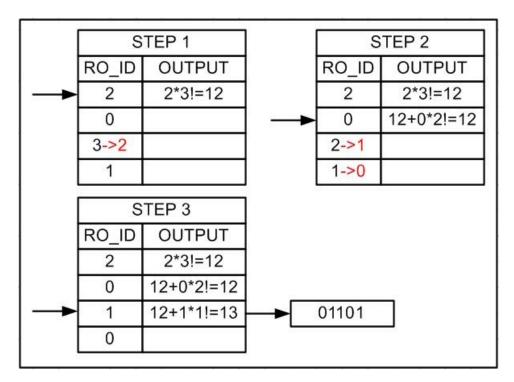

| Figure 5.11. | Output generation sample execution.                                           | 65 |

| Figure 5.12. | Ordering circuit sample execution                                             | 66 |

| Figure 5.13. | Output generation sample execution.                                           | 67 |

| Figure 5.14. | Output generation in pseudo code                                              | 67 |

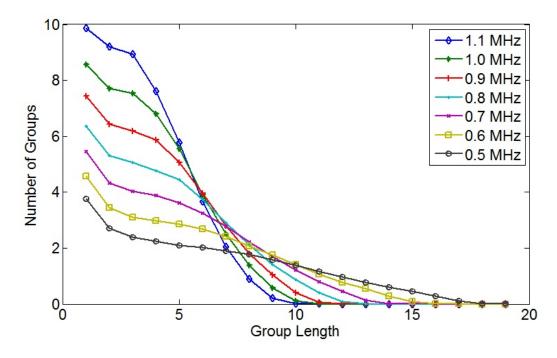

| Figure 6.1.  | Number of groups per group length for different $f_{thp}$ values              | 71 |

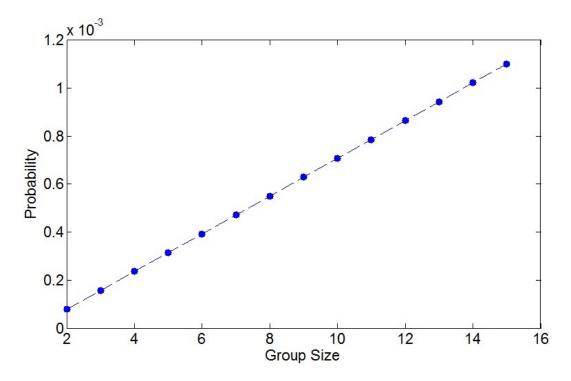

| Figure 6.2.  | Probability of two ROs to be placed in the same group                         | 73 |

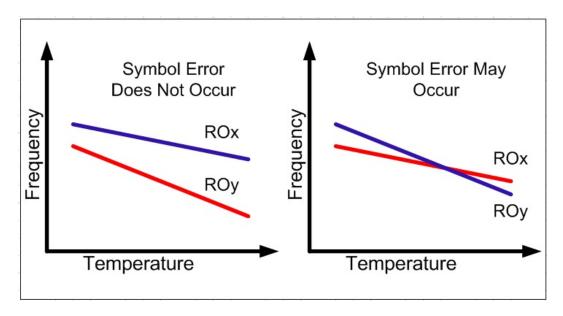

| Figure 6.3.  | Effect of ordering on symbol error [10]                                                            | 74 |

|--------------|----------------------------------------------------------------------------------------------------|----|

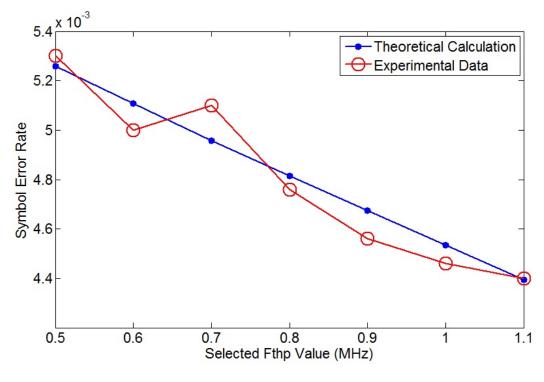

| Figure 6.4.  | Symbol error rate                                                                                  | 75 |

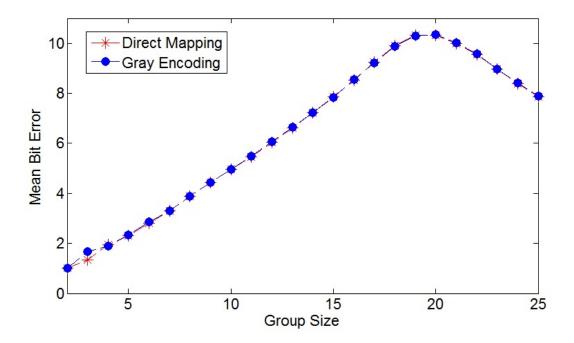

| Figure 6.5.  | Number of bit errors per group                                                                     | 77 |

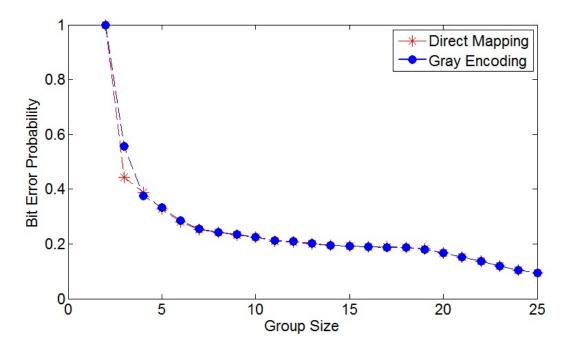

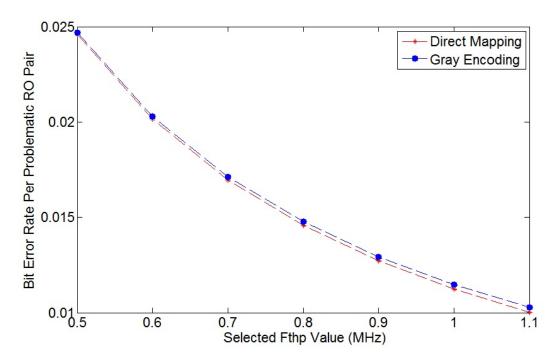

| Figure 6.6.  | Bit error probability per generated bit                                                            | 78 |

| Figure 6.7.  | Bit error probability per problematic RO pair                                                      | 79 |

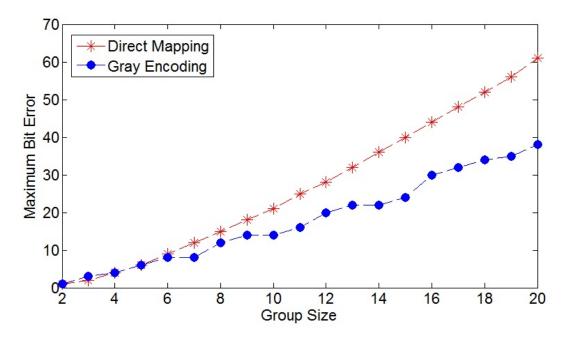

| Figure 6.8.  | Maximum error vs. group size                                                                       | 80 |

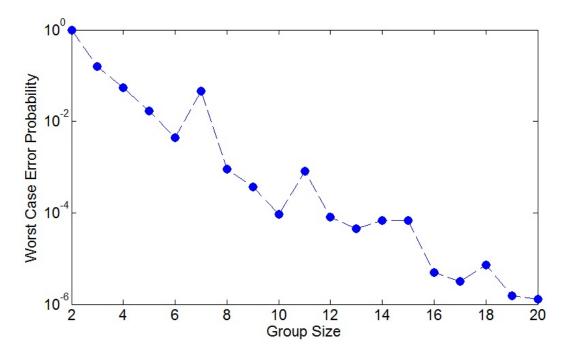

| Figure 6.9.  | Worst case symbol error probability vs. group size                                                 | 81 |

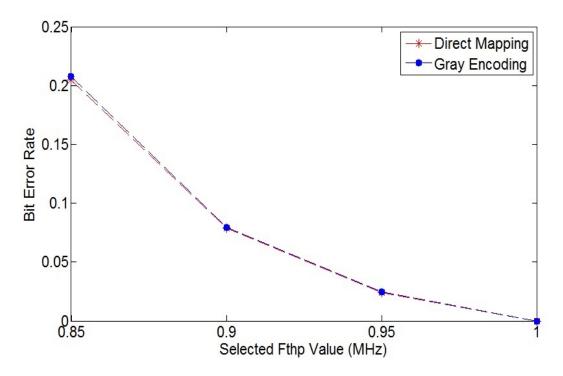

| Figure 6.10. | Bit error probability vs. $f_{thp}$ chosen                                                         | 82 |

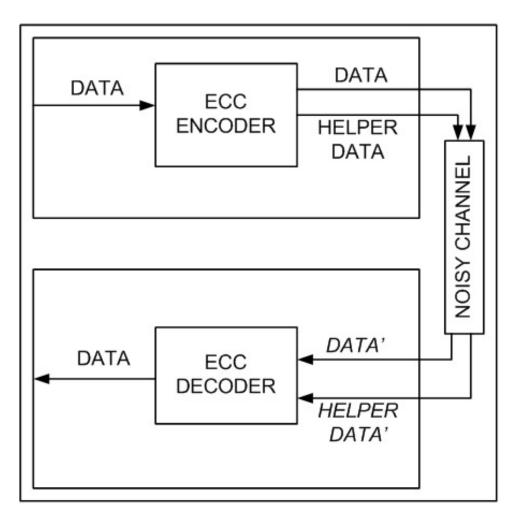

| Figure 6.11. | A system utilizing ECC.                                                                            | 84 |

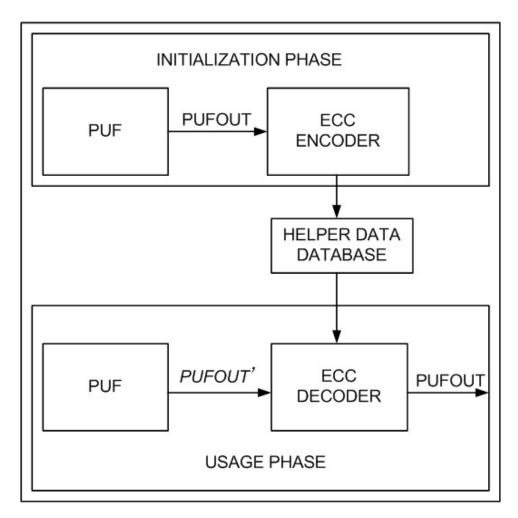

| Figure 6.12. | Use of ECC in PUF based systems                                                                    | 86 |

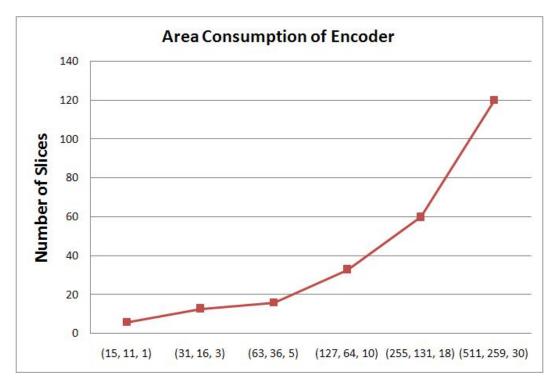

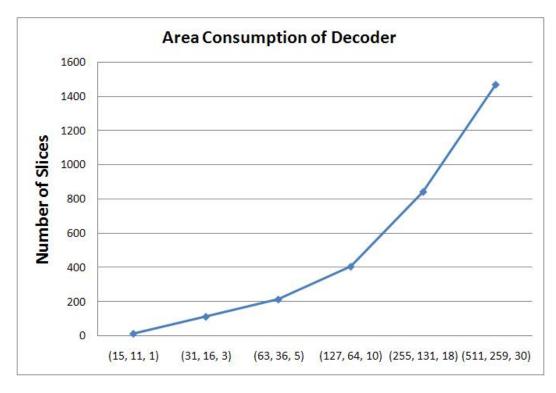

| Figure 6.13. | Area consumptions of BCH encoders with different data lengths<br>and error correction capabilities |    |

| Figure 6.14. | Area consumptions of BCH decoders with different data lengths<br>and error correction capabilities | 88 |

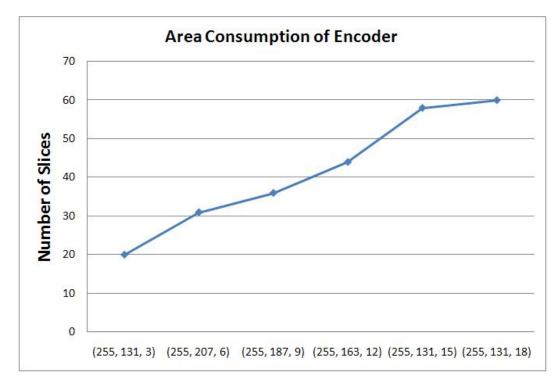

| Figure 6.15. | Area consumptions of BCH encoders with different error correction capabilities.                    | 89 |

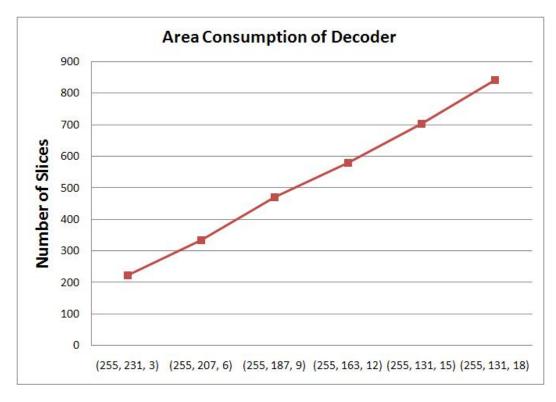

| Figure 6.16. | Area consumptions of BCH decoders with different error correction capabilities.                    | 90 |

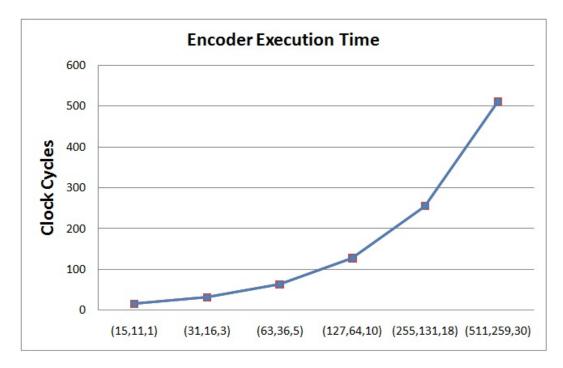

| Figure 6.17. | Execution times of BCH encoders with different data lengths and<br>error correction capabilities |

|--------------|--------------------------------------------------------------------------------------------------|

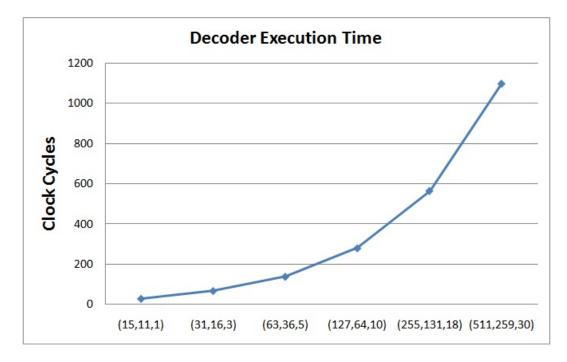

| Figure 6.18. | Execution times of BCH decoders with different data lengths and<br>error correction capabilities |

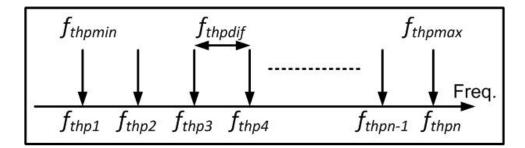

| Figure 7.1.  | The relation between the $f_{thpmin}$ , $f_{thpmax}$ , and $f_{thpdif}$ values 95                |

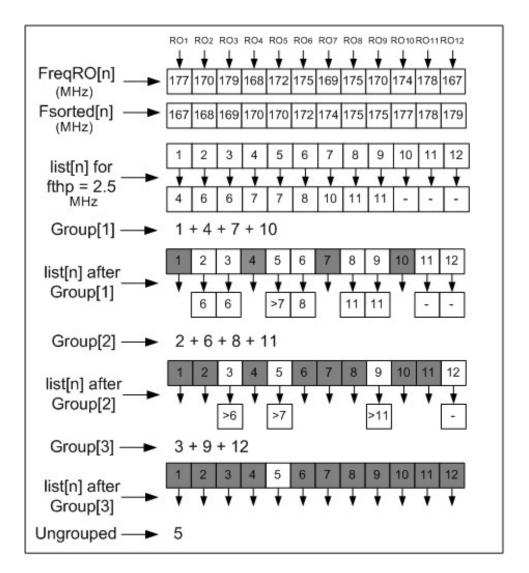

| Figure 7.2.  | DP sample execution for 12 elements with an $f_{thp}$ value of 2.5 MHz. 96                       |

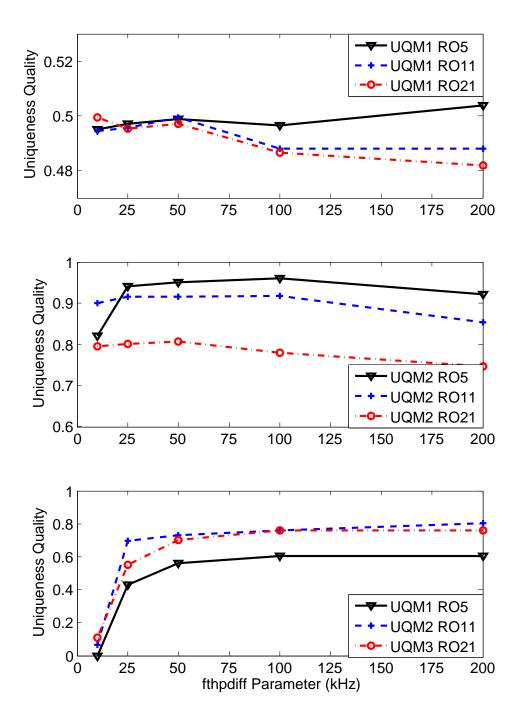

| Figure 7.3.  | Uniqueness Quality vs. $f_{thpdif}$ Parameter                                                    |

| Figure 7.4.  | Revised part of the DP algorithm in pseudo code 100                                              |

| Figure 7.5.  | DP algorithm sample execution for RO selection method 101                                        |

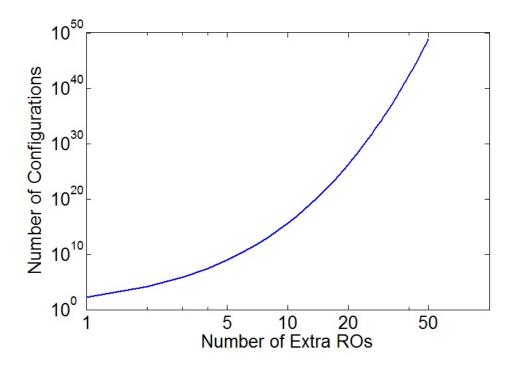

| Figure 7.6.  | Number of CRPs vs. additional ROs                                                                |

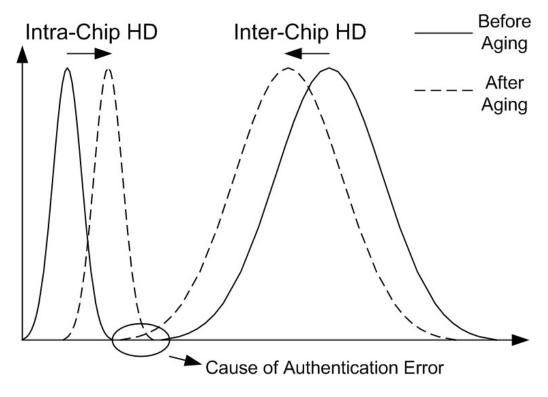

| Figure 7.7.  | Uniqueness quality vs. additional ROs                                                            |

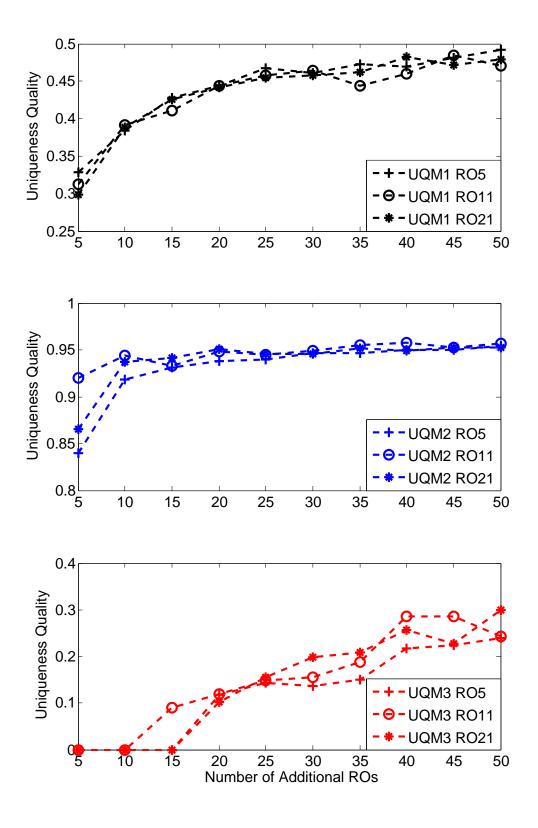

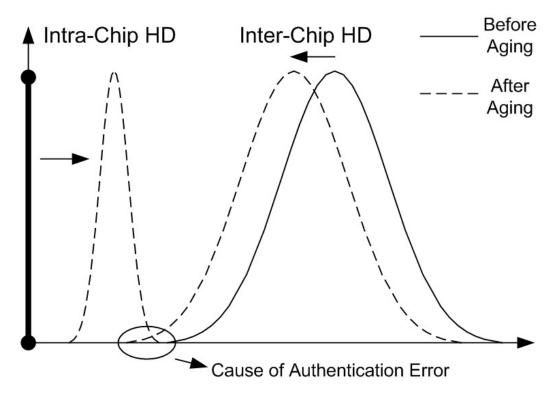

| Figure 8.1.  | Effect of aging on conventional PUFs                                                             |

| Figure 8.2.  | Effect of aging on ordering based RO-PUFs                                                        |

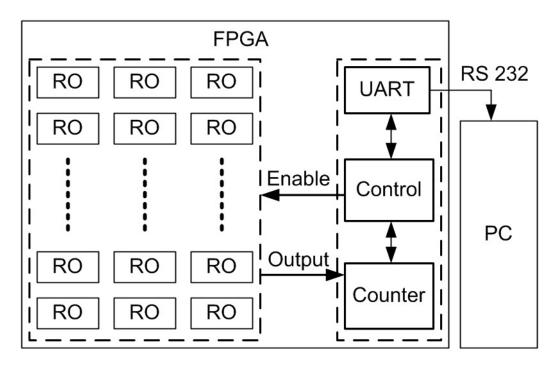

| Figure 8.3.  | Accelerated aging test setup                                                                     |

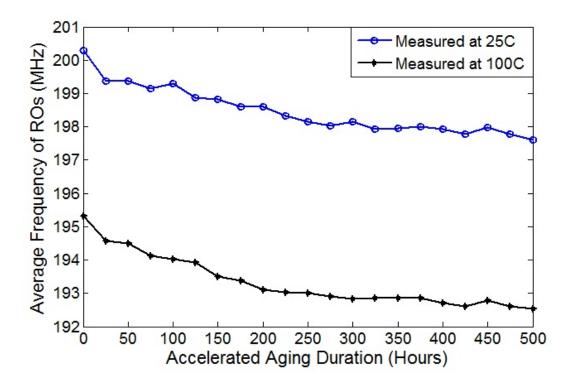

| Figure 8.4.  | Mean frequency of ROs vs. accelerated aging test duration 115                                    |

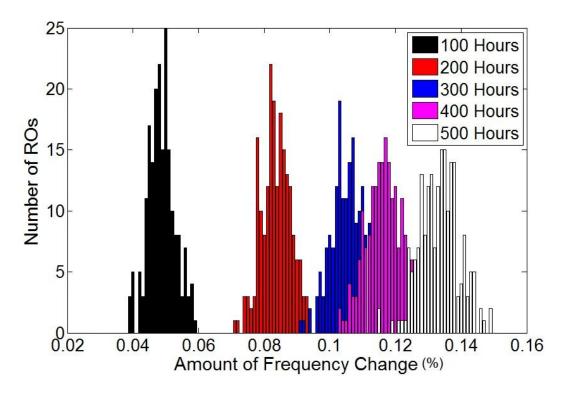

| Figure 8.5.  | Distribution of ROs depending on frequency reduction due to aging.116                            |

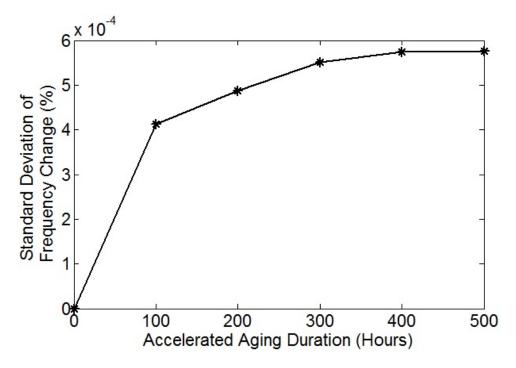

| Figure 8.6.  | STD of frequency reduction due to aging                                                          |

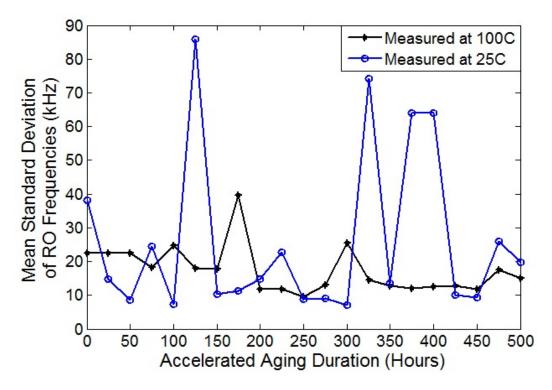

| Figure 8.7. | Noise on RO | frequency | measurements | vs. | aging. | <br> | • | <br>• | <br>118 |

|-------------|-------------|-----------|--------------|-----|--------|------|---|-------|---------|

|             |             |           |              |     |        |      |   |       |         |

## LIST OF TABLES

| Table 3.1. | Uniqueness and Robustness results of RO_PUF1 and RO_PUF2. $% \mathcal{A} = \mathcal{A} = \mathcal{A} + \mathcal{A}$ . | 35 |

|------------|-----------------------------------------------------------------------------------------------------------------------|----|

| Table 3.2. | Relation between the number of circuits to be identified, PUF out-<br>put length and security level.                  | 36 |

| Table 4.1. | Notations and Meanings                                                                                                | 47 |

| Table 5.1. | Maximum Frequency Deviation of ROs due to Temperature Change.                                                         | 60 |

| Table 5.2. | Area Reduction with DP                                                                                                | 62 |

| Table 5.3. | Uniqueness Results.                                                                                                   | 63 |

| Table 5.4. | Area Utilization of Frequency Detection Circuit.                                                                      | 64 |

| Table 5.5. | Area Utilization of RO-PUFs for Virtex5 Devices.                                                                      | 68 |

| Table 5.6. | Area Utilization of RO-PUFs for Spartan3 Devices                                                                      | 68 |

| Table 6.1. | Output Generation Mapping                                                                                             | 76 |

| Table 6.2. | Number of Problematic RO Pairs.                                                                                       | 81 |

| Table 6.3. | Simultaneous Symbol error probabilities for non-ideal $f_{thp}$ values                                                | 83 |

| Table 7.1. | $f_{thp}$ Selection Method Area Consumption vs. CRP count                                                             | 98 |

| Table 7.2. | Probability of Output Couples with HD Less than the Minimum<br>HD Defined         |

|------------|-----------------------------------------------------------------------------------|

| Table 7.3. | Minimum HD Among 128 bit Outputs within 10,000 CRPs Based<br>on the Number of ROs |

| Table 7.4. | Comparison of Ordering Based RO-PUFs in terms of Response<br>Uniqueness           |

| Table 8.1. | Equivalent IC Working Duration of Accelerated Aging Test 114                      |

| Table 8.2. | RO Frequency Reduction due to Aging vs. RO Location 116                           |

| Table 8.3. | Number of Problematic RO Pairs                                                    |

| Table 8.4. | Effect of Aging on $f_{thp}$ Parameter and Corresponding Area Overhead. 120       |

# LIST OF SYMBOLS

$f_{th}$  $f_{thp}$  Frequency Threshold Pre-determined Frequency Threshold

# LIST OF ACRONYMS/ABBREVIATIONS

| AAT                  | Accelerated Aging Test                                  |

|----------------------|---------------------------------------------------------|

| AES                  | Advanced Encryption Standard                            |

| ASIC                 | Application Specific Integrated Circuit                 |

| BCH                  | Bose, Chaudhuri, and Hocquenghem                        |

| BPUF                 | Butterfly PUF                                           |

| CMOS                 | Complementary Metal Oxide Semiconductor                 |

| CRP                  | Challenge-Response Pair                                 |

| DP                   | Dynamic Programming                                     |

| ECC                  | Error Correction Codes                                  |

| FAR                  | False Acceptance Rate                                   |

| $\mathbf{FF}$        | Flip-Flops                                              |

| FPGA                 | Field Programmable Gate Array                           |

| $\operatorname{FRR}$ | False Rejection Rate                                    |

| GVB                  | Gilbert-Varshamov Bound                                 |

| HCI                  | Hot Carrier Injection                                   |

| HD                   | Hamming Distance                                        |

| Hi-Z                 | High Impedance                                          |

| IC                   | Integrated Circuit                                      |

| ID                   | Identity                                                |

| IP                   | Intellectual Property                                   |

| LUT                  | Look-Up Table                                           |

| MV                   | Majority Voting                                         |

| NBTI                 | Negative-Bias Temperature Instability                   |

| NMOS                 | N-Type Metal Oxide Semiconductor                        |

| NVM                  | Non-Volatile Memory                                     |

| LISA                 | Longest Increasing Subsequence-Based Grouping Algorithm |

| NOC                  | Nominal Operating Conditions                            |

| PBTI                 | Positive-Bias Temperature Instability                   |

| PMOS | P-Type Metal Oxide Semiconductor            |

|------|---------------------------------------------|

| PS   | Patience Sorting                            |

| PUF  | Physical Unclonable Function                |

| RFID | Radio Frequency Identification              |

| RO   | Ring Oscillator                             |

| RV   | Random Variable                             |

| SRAM | Static Random Access Memory                 |

| STD  | Standard Deviation                          |

| TDDB | Temperature-Dependent Dielectric Breakdown  |

| UART | Universal Asynchronous Receiver/Transmitter |

| VT   | Varying Temperature                         |

### 1. INTRODUCTION

#### 1.1. Motivation

Physical Unclonable Functions (PUFs) are recently proposed circuit primitives that are utilized mainly in security applications. PUFs provide the ability of creating chip specific signatures depending on the small mismatches present in the IC. Even though several different structures are developed and an important amount of work is presented in the literature, PUFs are still far from maturity and the subject requires significantly more work to be done.

One major gap in the literature pertains to the reliability of PUF circuits. Widely accepted and standardized evaluation methods of PUF circuits are not present in the literature. Therefore, performance of the structures are generally measured with basic formulations that do not maintain reliable evaluation results. 100% robust output generation is problematic for PUF circuits due to their noisy nature. Ordering based Ring Oscillator (RO) PUFs did not receive much attention in spite of their ability to generate reliable outputs and provide high entropy extraction even in Field Programmable Gate Array (FPGA) environment. Challenge-Response Pair (CRP) concept, which is very important for certain type of applications, such as authentication, has also not yet been defined for ordering based RO-PUF circuits. Attacks on PUF circuits and attack resistant designs are also productive research areas. Effects of aging on PUF circuits, an important topic to study the long term behavior of these circuits, is another area that drew little attention in the literature yet. In addition to the topics mentioned, PUFs require more work in many aspects for better performance and widespread usage. In the scope of the thesis, many of these issues are addressed and significant improvements in the design and evaluation of PUFs are achieved.

#### 1.2. Contributions and Organization of the Thesis

The thesis is composed of 9 chapters. Organization and contributions of the thesis can be summarized as follows.

Chapter 2 focuses on the background of PUFs. Definition of PUF is given and applications utilizing these circuits are presented. Next, PUF properties, uniqueness, robustness, unclonability, and unpredictability are discussed. The chapter is concluded by presenting the standard PUF types proposed in the literature.

In Chapter 3, quality metrics for the uniqueness and robustness properties of PUF circuits are derived for a fair performance evaluation. Next, confidence interval and confidence level concepts are adapted to PUF evaluation in order to maintain the trustworthiness of the performance results. Then, two basic RO-PUF structures proposed in the literature are implemented in FPGA environment. Finally, outputs of both of the structures are collected using serial port and analyzed in Matlab environment according to the proposed quality metrics.

Theoretical foundations of ROs are discussed in Chapter 4. Based on these theoretical foundations, optimization techniques for the number of stages and measurement time of the RO-PUF structures are presented. Then, proposed techniques are validated using real implementation results collected from FPGAs. Based on the theoretical foundations and analysis results, optimum number of stages and measurement time are determined for best performing RO-PUF structures.

Maximizing the robustness and entropy extraction in RO-PUF structures are discussed in Chapter 5. Dynamic programming (DP) is adapted to ordering-based RO-PUF structures and its lower complexity compared to previous approaches is proved. Finally, the effectiveness of the proposed approach is validated via experimental analysis.

Chapter 6 focuses on error probability and correction in ordering based RO-

PUFs. First, a systematic analysis of bit error probability is presented. Then, the area consumption and robustness relation is discussed. Finally, Bose, Chaudhuri, and Hocquenghem (BCH) codes, which are multi-bit correcting type Error Correction Codes (ECC), are implemented due to their suitability for error correction in PUF circuits. Their area consumption and timing performances are analyzed for different output lengths and error correction capabilities.

CRP concept is presented in Chapter 7. CRP properties and importance of large number of CRPs are discussed in the first section. Two CRP enhancement methods,  $f_{thp}$  selection and RO selection, are proposed to overcome the drawbacks of small number of CRPs in RO-PUFs. With these methods, shortage of CRPs in RO-PUFs is eliminated with reasonable area overhead.  $f_{thp}$  selection and RO selection methods are compared in terms of CRP quality, area consumption, and timing efficiency.

Aging mechanisms and effects of aging on PUFs are discussed in Chapter 8. The results of an Accelerated Aging Test (AAT) applied in FPGA environment to determine the behavior change of ROs due to aging is presented. Effects of aging on ordering based RO-PUFs are analyzed and a compensation mechanism to maintain 100% reliability even after long years of operation is proposed. Finally, Chapter 9 concludes the thesis.

### 2. PHYSICAL UNCLONABLE FUNCTIONS

#### 2.1. Definition and Applications

PUF is a relatively new concept introduced by Pappu *et al.* in 2001 [11,12], which has the unique capability of generating chip specific signatures during operation. Their unclonability is a result of uncontrollable components present in the manufacturing process, such as oxide thickness, threshold voltage, or doping concentrations. Since it is impossible to replicate these process variations in another die, generated signatures are unique and chip specific. Unclonability, uniqueness, robustness, and unpredictability are the main features that each PUF should provide. In addition to these, they should be easy to evaluate and hard to characterize [13].

PUFs provide efficient solutions to security related problems. IP protection, authentication, identity (ID) generation, and cryptographic key generation can be considered as the main application areas that PUF circuits provide powerful solutions [14]. The main advantages of PUFs over conventional techniques are their low cost, ease of integration, and resilience against physical and side channel attacks [4]. In addition to these, they eliminate the need for non-volatile memory and a secure channel to the device for ID or key storage, which improves the security of the system significantly [1]. PUFs also do not require any special manufacturing, programming, or testing steps and some PUF structures are also suitable for FPGA implementations as well.

PUFs can be divided into two types; CRP supporting and CRP non-supporting. CRP non-supporting systems generate outputs without using any input applied to the circuit. In these systems, a single bitstream is generated by each implementation of the structure. In CRP supporting systems, outputs (responses) are generated depending on the applied inputs (challenges), in addition to the intrinsic characteristics of the circuit. In this context, CRP supporting PUFs can be defined as a mathematical function that maps challenges  $C_i$  to responses  $R_i$ , which can be written as  $R_i \Leftarrow$

Figure 2.1. CRP supporting and non supporting PUFs.

$PUF(C_i)$ . CRP supporting and non-supporting PUFs are illustrated in Figure 2.1.

PUFs have been utilized in many security related applications after the first successful implementations were realized. Authentication via CRPs is an effective solution provided by PUF circuits. Authentication is performed in two phases when PUFs are employed. In the initialization phase, a number of CRPs are stored in a secure database. In the usage phase, a challenge that is already recorded in the database is sent to the device by the application that needs to verify the system. Then, the response of the device is compared with the response on the database. If the responses match, the device is considered to be authentic. In this system, each CRP should only be used once to prevent the success of replay attacks [2]. Authentication is illustrated in Figure 2.2.

By removing the noise present in the outputs, PUFs can be used as cryptographic key generators as well. Using the keys generated by the PUF circuit, all security applications utilizing standard symmetric and asymmetric cryptographic techniques can be employed [15, 16]. Generating the key using a PUF eliminates the need for storing the key on a battery-backed random access or non-volatile memory, decreasing the cost significantly. In addition to these, probability of theft of the key is significantly

Figure 2.2. PUF based authentication [1].

reduced, since the key is deleted from the system immediately when used by the cryptographic algorithm. Generating the key on another device is also impossible due to the unclonability property of PUFs, which maintain the system security [17,18]. A sample scheme for key generation is illustrated in Figure 2.3.

Intellectual Property (IP) protection is another area that PUF circuits are employed. Since bitstreams are loaded to FPGAs every time the system is powered-up, intruders may copy the bitstream via using a logic analyzer or oscilloscope. With this method, IPs can be used in other systems without the information of the IP developer. Loading bitstreams to the FPGA in an encrypted form and decrypting the IP using the key that is already loaded to the device is a proper method against IP theft [17,19]. Generating the key on the fly using PUF is an efficient and secure way for such systems with the advantages discussed in the previous paragraph. As an alternative, public key authentication system for IP protection is proposed in [20]. In public key based IP protection systems, public key does not leave the device in any case; hence, increasing the system security.

PUF circuits are utilized for identification as well. In systems such as Radio Frequency Identification (RFID) ICs, IDs can be generated by PUFs, since they have

Figure 2.3. Cryptographic key generation with PUFs [1].

important advantages over traditional mechanisms. For instance, an attacker can easily copy the ID of one integrated circuit (IC) to another, which is not possible when the ID is generated by PUFs. In simple RFID tags, cloned tags are not distinguishable from authentic ones [21]. In addition to the areas that are mentioned so far, PUFs are used in different areas such as vehicle system security, seals for insurance applications [22], and error detection methods in finite state machines as well [23].

#### 2.2. PUF Properties

#### 2.2.1. Uniqueness

Uniqueness, which is also called inter-PUF variation, is the variation of the outputs generated by the same PUF structure on different IC instances. Ideally, outputs collected from different ICs should be statistically independent and uniformly distributed. In such a system, no correlation is present between different outputs. If the uniqueness property of a PUF is weak, different ICs may generate similar responses and identifying different circuits will not be possible. Highly unique outputs are very important for a system that utilizes PUF circuits to maintain security. The major quality metric for uniqueness is the inter-PUF Hamming distance (HD), which can be calculated as

$$U_{-}QM1 = \frac{2}{k(k-1)} \sum_{i=1}^{k-1} \sum_{j=i+1}^{k} \frac{HD(R_i, R_j)}{n},$$

(2.1)

where k is the total number of outputs collected from different ICs,  $R_i$  is the response of *ith* circuit, HD is the Hamming distance function, and n is the total number of HD operations. The ideal value for  $U_{-}QM1$  is 0.5.

#### 2.2.2. Robustness

Robustness, which is also called intra-PUF variation, is related to the number of bits that change value between different readings from the same IC. In an ideal system, intra-PUF variation should be zero, meaning that the outputs collected from the same circuit should be the same, independent of time and environmental conditions. However, since the outputs generated by PUF circuits depend on small mismatches present in the internal characteristics of the IC, environmental variations, such as temperature, supply voltage, and crosstalk may lead to generation of unreliable bits in the outputs collected consecutively [24]. The major quality metric for robustness is the inter-PUF HD, which can be calculated as

$$R_{-}QM1 = \frac{1}{x} \sum_{y=1}^{x} \frac{HD(R_i, R'_{i,y})}{n},$$

(2.2)

where x is the total number of consecutive measurements from the same IC,  $R_i$  is the reference response of the IC,  $R'_{i,y}$  is the yth output collected, and n is the total number of HD operations. The ideal value for  $R_QM1$  is 0.

Since noisy data is not acceptable for applications such as cryptographic key generation, applying appropriate post-processing techniques such as ECC and extraction algorithms are required for noise-free output generation [25]. However, post-processing techniques decrease the area, time, and power efficiency of the system, and increase the complexity significantly. These overheads are also very dependent on the amount of unreliable bits at the output. Therefore, generating higher quality PUF responses is another aim of designers to minimize the post-processing cost. An alternative PUF structure that generates noise-free outputs without the need of ECC is presented within the scope of this work.

#### 2.2.3. Unclonability

Unclonability is a fundamental behavior of PUFs that indicates the impossibility of building two identical PUF circuits that respond similarly to the same challenges. In addition to this, unclonability property indicates that it is very hard, time consuming, and practically impossible to build an accurate mathematical model of a PUF that will enable computation of the responses to the challenges, without using the PUF itself. The core of the unclonability property of PUFs is the uncontrollable process variations present in the system.

#### 2.2.4. Unpredictability

Unpredictability is another key feature of PUF circuits. According to the unpredictability principle, even if the environmental conditions, structure, and layout of a PUF are known, responses to the challenges should be still unpredictable. In addition to this, the system should maintain that even if infinitely many CRPs are known, response to a new challenge should be still unpredictable. If the unpredictability property of the utilized PUF structure is low, system security will be threatened.

Figure 2.4. Optical PUF measurement setup and pattern from a silicon surface [2].

#### 2.3. PUF Types

#### 2.3.1. Optical PUF

Optical PUF is the first structure developed in the name of physical one-way functions in 2001 [11,12]. In this structure, bubble filled transparent epoxy is applied on top of the wafer and laser is shined on the sample to create a speckle pattern. Since this pattern is dependent on the material and thickness of the wafer, and the property and distribution of the epoxy, different ICs will have unique reflections that enable the generation of unique signatures. Even though a large number of CRPs can be generated via Optical PUFs by changing the wavelength, angle, or position of the laser, they are not very practical to use in the field, since measurement devices are quite complicated.

Reconfigurability is an advantage of optical PUFs, which enables changing the signature or key permanently when needed [26]. Reconfigurability is achieved via applying a high energy laser beam to the IC, which changes the optical properties of the epoxy. An optical PUF measurement setup and a pattern recorded from a silicon surface are presented in Figure 2.4.

#### 2.3.2. Coating PUF

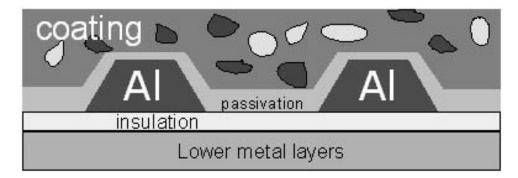

Coating type PUF was presented in 2006 [3]. In this structure, the IC is covered with a protective matrix coating doped with random dielectric particles. Then, a top

Figure 2.5. Schematic cross-section of a coating PUF [3].

metal layer is built on top of the IC to measure the local capacitance of the coating. Measured capacitance value is used to characterize the circuit and generate the unique signature of the device. Schematic cross-section of a coating PUF is illustrated in Figure 2.5. It is shown in [3] that 600 bits/mm<sup>2</sup> of signature can be generated using 200 capacitance sensors/mm<sup>2</sup>. The main disadvantage of this method is its impracticality due to the requirement of additional processing steps that complicates the implementation and increases the cost.

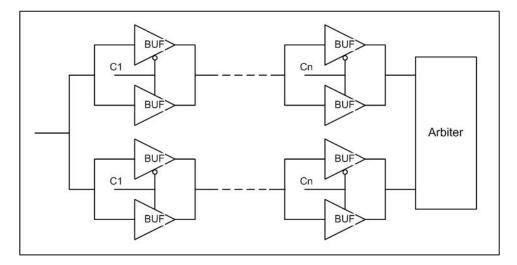

#### 2.3.3. Arbiter PUF

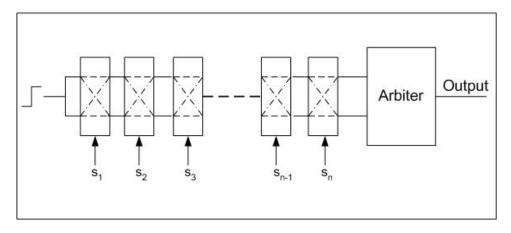

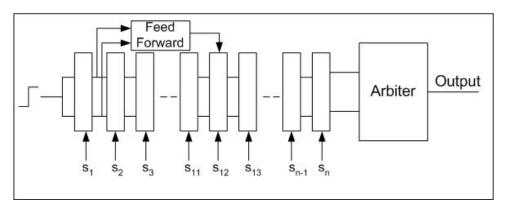

Varying timing behavior of elements on ICs are the basis for Arbiter PUF structures presented in [27, 28]. In arbiter PUFs, a number of delay elements that construct two parallel paths are connected serially and a rising signal is applied to both paths [29, 30]. At the end of these paths, an arbiter determines the signal that arrives at the other end faster and generates a one bit response as shown in Figure 2.6. In arbiter PUFs, multiplexers are used as delay elements to carry the input signals to the outputs. According to the value of the select signal that controls both of the multiplexers, one input passes through the first gate and the other passes through the second gate or vice versa. The challenge applied to the arbiter PUF determines the path that the signals will follow and the response will be one bit 0 or 1, based on the arrival ordering of the two input signals. Arbiter PUF generates 2n possible delay paths using n delay elements. In order to generate an m bit response, this structure can be duplicated m times or alternatively, m serial measurements can be taken by applying m different challenges.

Figure 2.6. Arbiter based PUF circuit.

Figure 2.7. Feed-forward arbiter based PUF.

The main problem of arbiter based structures is their vulnerability against modeling attacks. The attacker may solve the behavior of a PUF after collecting a certain number of CRPs [31, 32]. To overcome this problem, feed forward arbiter structure was presented by Lim *et al.* [29]. With this scheme, non-linearity is added to the PUF to harden the modeling attacks as illustrated in Figure 2.7. According to the analysis presented, feed forward arbiter PUF structure has an inter-PUF variation of 38% and an intra-PUF variation of 4.5%. It is also reported that the maximum working frequency is 100 MHz and the power consumption of an 8 bit PUF is 137  $\mu$ W with 0.18  $\mu$ m TSMC process.

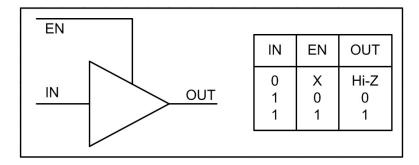

Tristate buffer based PUF is very similar to the arbiter PUF and it was proposed by Sunar *et al.* in 2008 [33]. In this structure, a certain number of switches are connected serially and each switch is controlled by one bit of the challenge in a similar fashion. The main difference from the multiplexer based structure is the type of the

Figure 2.8. Tristate buffer and truth table.

Figure 2.9. Delay unit in tristate buffers.

switch element. In this circuit, two tristate buffers are used to build the switch, rather than using multiplexers. The signals are routed through separate lines in the switch element, instead of interleaved routing within the multiplexer. Tristate buffers have three output states as 1, 0, and high impedance (Hi-Z), as shown in Figure 2.8.

Outputs of the two tristate buffers are connected to build a delay element with two possible paths. However, if both buffers become active at the same time, the circuit is under risk of being short circuited. To prevent such a condition, enable signals of two buffers should be complements of each other. In this case, the input signal will pass through either one of the buffers as illustrated in Figure 2.9.

In the next step, two parallel delay paths are constructed by cascading the delay units serially. Finally, the inputs of these delay lines are connected to each other and the outputs are fed to an arbiter. The arbiter is designed as a single Flip-Flop

Figure 2.10. PUF architecture built with tristate buffers.

(FF), whose data and clock inputs are connected to the outputs of the delay lines. According to the delay difference of the paths, the output of the FF gets the value of 1 or 0. The schematic diagram of the proposed structure is presented in Figure 2.10. The advantage of a tristate buffer based PUF compared to the arbiter PUF proposed in [29] is its 20% lower power and area consumption. Reliability problem is not considered in this work.

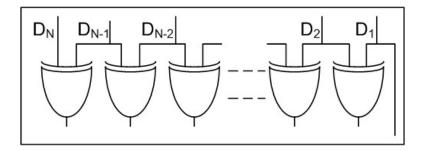

One of the ways suggested to overcome the vulnerability of arbiter PUFs against modeling attacks is to add input and output networks shown in Figures 2.11 and 2.12 to the system [4,34]. The aim in the proposed method is to prevent the attacker from reaching the inputs and outputs of the arbiter PUF directly. Another countermeasure presented in the paper is to remove the PUF from the FPGA after the configuration is complete. This prevents the attacker from collecting enough number of CRPs from the structure. In addition to these, attack types are classified and system level countermeasures against modeling are also discussed with some mathematical background on the subject.

#### 2.3.4. Glitch PUF

Glitch PUF, which is another PUF type that exploits the delay variation of circuits, was first presented by Suzuki *et al.* in 2009 [35]. In a glitch PUF, a certain

Figure 2.11. Input network [4].

Figure 2.12. Output network [4].

set of input vectors is utilized as challenges and applied to a complex logic block known as glitch generator, and glitches at the output are sampled via registers. Since the delay of interconnects and gates will vary from die to die, different ICs will generate uniquely shaped glitches. In this structure, the logic block should be complex enough to generate enough entropy for valid response bits. For instance, Advanced Encryption Standard (AES) S-box is a proper block for glitch generation due to its complexity. Delay circuits that are used to convert the glitch shapes to output bitstream are also presented in the cited work. In addition to these, a technique based on standard delay format simulation is also presented to model the structure before manufacturing. According to the analysis presented, glitch PUF shows an average inter-PUF HD of 41.5%, and an average intra-PUF HD of 1.3% under Nominal Operating Conditions (NOC).

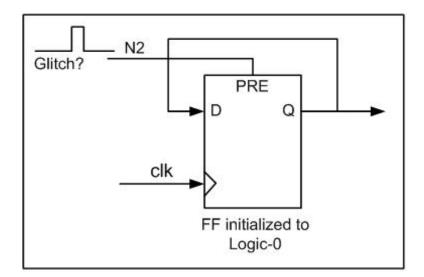

Two different versions of the glitch PUF are presented by Patel *et al.* in [36–38]. In the first method, glitch counts are used as unique signatures. In this way, either counter approach or one hot state shift register approach is used to count the glitches. The second method presented is to sample the output of the glitch generator by one of the glitches within the specified block. In these works, a multiplier is used as the glitch generator and input patterns are analyzed to achieve reliable and unique outputs. Stability analysis and improvement methods are also discussed.

#### 2.3.5. Memory Based PUF

2.3.5.1. SRAM PUF. Static Random Access Memory (SRAM) PUF is PUF type that utilizes SRAM in the circuit. Complementary Metal Oxide Semiconductor (CMOS) SRAM is a device with six transistors [39]. Four of the transistors are connected to form two cross-coupled inverters that will hold the stored value and two transistors are used as the load transistors to drive the value applied from outside to the cross coupled inverters. During write operation, the value stored in the SRAM may change, otherwise stable operation is maintained. However, any external signal is not applied to the inverters during power up. Therefore, the value of an SRAM cell will tend to be 0 or 1, depending on the minor voltage differences and mismatches between the two inverters. Since internal parasitics are mostly stable within the IC, SRAM outputs will be the same after consecutive power-ups with high probability. However, internal parasitics are different among ICs and initial condition of SRAM value will differ within different ICs. Based on these properties, SRAM can be used as a PUF [40].

The main advantage of an SRAM PUF is its convenient structure for FPGA implementations [19]. Most of the FPGAs that are in use today include built-in SRAM memory blocks that can be used to store data. However, some of the SRAMs in these products have initial conditions that prevent them from having random values during startup. These types of FPGAs do not allow SRAM PUF implementations.

One of the most important advantages of SRAM PUF is its ease of use since no evaluation circuitry is needed. Since SRAM bits get their value during power up immediately, only read operation is performed to get the output. In this sense, the required key or signature is generated in a short time compared to other PUF structures such as RO-PUF or Arbiter PUF. Another work that focuses on SRAM PUF is presented in [41]. In this work, crosscoupled NOR structures are utilized as the memory element and Application Specific Integrated Circuits (ASICs) are manufactured rather than using FPGA environment. The main aim of the cited work is to minimize the power consumption.

Finally, a solution to the problem of FPGAs that have initialized FFs is presented in [42]. In the proposed method, initialization flow of FPGAs is modified by changing the bit file to remove the initialization step of FFs. Then, the values that have been settled in the FFs are read out to be used as PUF output. Next, the FFs are initialized again and normal operation flow is continued. According to the results that are presented in the paper, an important amount of post-processing is required to achieve unique signatures due to the present bias at FF output values.

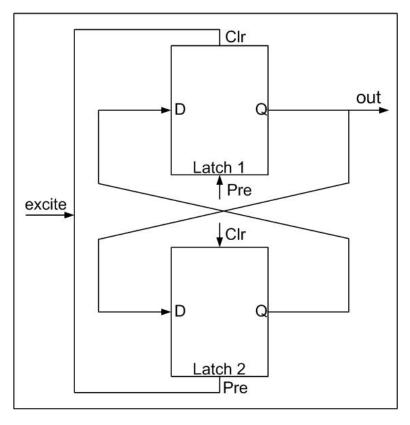

2.3.5.2. Butterfly PUF. Cross-coupled structures are basic building blocks of many storage elements such as SRAMs and FFs. Due to positive feedback induced by the loop, the stored value is retained as long as the supply voltage is present. Butterfly PUF (BPUF) is a structure that behaves similarly to SRAM memories during the power-up phase [5]. BPUF cells are composed of two latches that can be forced to an unstable operating point during the PUF operation. When the latches are released, output of one of the latches can be used as PUF output. BPUF operation is illustrated in Figure 2.13.

The main advantage of BPUF over SRAM PUF is its suitability for all FPGAs [43]. Even though the structure is supported by every FPGA, it is not straight-forward to build BPUF due to the symmetric routing required. Automatic placement and routing cannot achieve proper layout for BPUF implementation. Therefore, manual routing is required. If symmetric routing cannot be achieved, the output of the BPUF cell will be the same on every FPGA and violate the uniqueness property.

According to the results presented in the paper, inter-PUF HD is around 50%, which is the ideal case for PUF structures and 6% of the output bits behave unreliably

Figure 2.13. BPUF operation [5].

during the temperature change from  $20^{\circ}C$  to  $80^{\circ}C$  and  $-20^{\circ}C$  to  $20^{\circ}C$ .

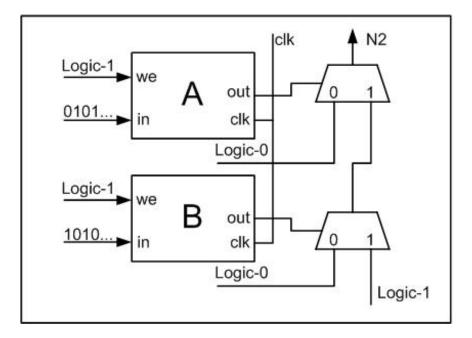

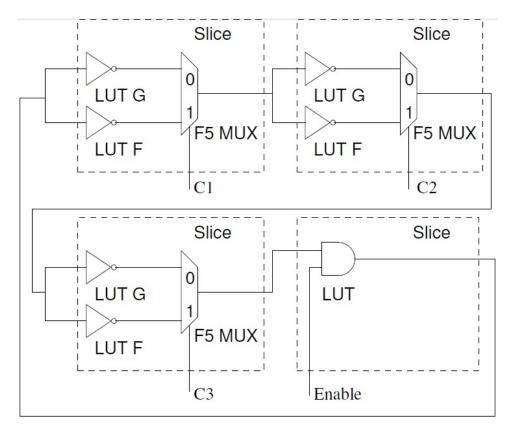

### 2.3.6. RST PUF

A novel PUF design called RST-PUF, which can be built on look-up table (LUT) based FPGAs, is proposed by Anderson *et al.* [6]. In this method, LUTs are configured as shift registers and two LUTs generate one bit PUF response, as illustrated in Figure 2.14. With the rising edge of the *clk* signal, output of each multiplexer switches and depending on the speed differences of the multiplexers, a glitch is generated at the output. This glitch is used to generate one bit PUF output, as shown in Figure 2.15. This structure is implemented just using VHDL coding. Manual place and route is not required, since the whole structure is within a slice and no external routing is required. According to the reliability analysis, 3.6% of the bits are unreliable under changing temperature conditions. This result is similar to many other PUF structures presented.

Figure 2.14. LUT based RST-PUF circuit [6].

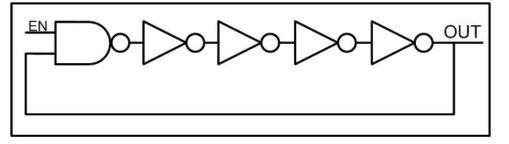

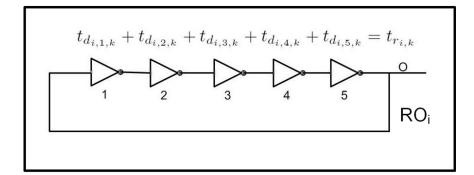

#### 2.3.7. Ring Oscillator PUF

RO type PUFs that utilize the delay differences of identical structures were first presented by Gassend *et al.* in 2002 [13]. In the cited work, a continuously oscillating variable delay circuit is built. In this circuit, the delay and the frequency of the oscillating loop changes according to the applied challenge. The frequencies of the variable delay circuit are used to generate the PUF outputs afterwards.

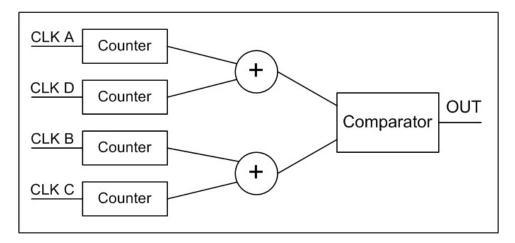

In regular RO-PUFs, the output depends on the frequencies of two identical ring oscillators. In this system, one bit response is generated by comparing two ROs. For instance, the output bit can be defined as 0 if  $RO_1$  is faster than  $RO_2$  and can be defined as 1 if  $RO_2$  is faster than  $RO_1$ . Since a PUF structure is expected to generate a certain length bitstream, a number of identical ROs are implemented in the circuit and different pairs are selected for each output bit generation via multiplexers. The mechanism to compare the oscillation frequencies of ROs is to utilize counters that will count the number of transitions of the selected ROs in a certain time interval. Finally, a comparator is used to determine the counter with the higher value and produce one bit output accordingly. A five stage RO with enable input is illustrated in Figure 2.16. The reason for using an enable input at the RO is to suspend the ROs that are not

Figure 2.15. RST PUF output generation [6].

Figure 2.16. 5-stage RO schematic with enable input.

being measured to prevent inter-locking of ROs. The whole system is illustrated in Figure 2.17.

Similar to other silicon PUF types, RO-PUFs are vulnerable to environmental conditions as well. Temperature and supply voltage variations are the main sources of unreliable behavior of RO-PUFs. Due to environmental variations, frequency ordering of two ROs, whose frequencies are very near to each other, may flip as illustrated in Figure 2.18. In addition to these, due to the noise present in the system, two consecutive measurements may differ as well even under the same conditions. To overcome this problem, different structures are presented in the literature.

One of the proposed methods is to group more than two ROs and select two of them whose frequencies are far enough from each other as presented in [1]. In this design, eight ROs are grouped and two of these, which are better separable from each

Figure 2.17. PUF output bit generation by conventional systems.

Figure 2.18. Effect of temperature variations on RO-PUF.

other are selected to generate the response bit. In this scheme n/8 bits are generated for n ROs. The main problem of this scheme is its high hardware cost, since n/8bits are generated using n ROs. Via this approach, 46% inter-PUF HD and 0.48% intra-PUF HD is achieved. A similar approach utilizing the components within the slices is presented in the name of Configurable RO-PUF [7]. Using three select signals, eight different RO configurations are implemented, as shown in Figure 2.19. Then, the configuration resulting in the highest frequency difference between the two ROs of a pair is selected for generating reliable outputs. The same scheme is improved in [44] by generating 256 different configurations with eight select signals. Both of the methods offer higher reliability without area overhead.

Figure 2.19. Configurable RO-PUF scheme [7].

A more complex, but hardware efficient solution to overcome the robustness problem of RO-PUFs, which is called Temperature-Aware Cooperative RO-PUF, was presented by Yin *et al.* in 2009 [10]. As discussed above, the faster RO within a pair may become the slower one because of the temperature or voltage variations. This will lead to generation of unreliable response bits; hence, resulting in the degradation of robustness. The proposed scheme depends on measuring the frequencies of RO couples just after manufacturing and defining rules for bit generation. These rules basically define the temperature ranges for each RO pair so that reliable bits are generated, and alternative pairs for the temperature ranges that may lead to erroneous output generation. For instance, for temperatures below  $t_1$ ,  $RO_1$  is faster than  $RO_2$ , for temperatures above  $t_2$ ,  $RO_2$  is faster than  $RO_1$ , for temperatures between  $t_1$  and  $t_2$ , reliable bit generation is not possible with these two ROs and other ROs should be involved in the generation of this particular bit in that range. The main advantage of this method is its high robustness in unstable temperature conditions. The drawbacks are the need for temperature sensor, memory for storing the rules for bit generation, and long initialization time to generate the rules for each IC manufactured. In addition to these, the effect of voltage variation is not considered.

In [7,45,46], Maiti *et al.* proposed ways to improve the uniqueness and reliability of RO-PUFs. According to the cited works, frequencies of ROs at different regions of FPGA tend to differ more than the ones adjacent to each other. This behavior is a factor that decreases uniqueness, if the comparison is done between the ROs that are implemented at different regions. The proposed solution is to compare the ROs that are located next to each other. In addition to these, a mathematical model of regular RO-PUFs is built and a large scale characterization is done using 125 FPGAs. According to the analysis presented, RO-PUF shows an average inter-PUF HD of 47.31%, and an average intra-PUF HD of 0.86% under NOC.

Systematic variations of ICs are investigated and mathematical model of RO-PUFs is updated in [47]. In this work, it is shown that systematic variations are mainly caused by power supply variations and these can mask the manufacturing variability and decrease the uniqueness of RO-PUFs significantly. Under these circumstances inter-PUF HD of RO-PUF systems implemented on FPGAs may decrease down to 32% for certain cases, which is not acceptable for many PUF based applications.

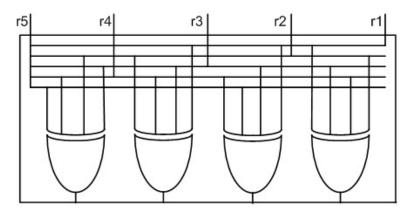

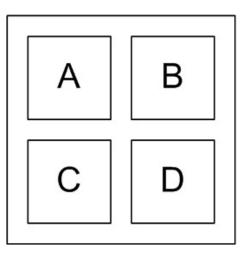

Another technique to improve reliability is presented in [8]. In this work, the resources of the FPGA are used in a way to decrease the effects of spatial gradients like doping concentration. In order to achieve this, four neighboring ROs are arranged in a square, occupying the same LUT position in their individual configurable logic blocks, as shown in Figure 2.20. Then, the oscillation counts of the crosswise ROs are added and output bit is generated according to the comparison of additions, as shown in Figure 2.21. To improve the reliability performance of the proposed structure, a threshold value is determined and the measurement is repeated as long as the difference between the comparator input values is below the threshold value. According to the analysis presented, increasing the threshold value improves the robustness performance of RO-PUFs. However, since more measurements are required, timing performance of the structure is degraded.

Figure 2.20. Location of ROs used for 1 bit generation.

Figure 2.21. Output generation mechanism proposed in [8].

PUF types summarized in this section do not involve all structures proposed in the literature. Only the structures that have drawn significant attention are presented. Reconfigurable PUF [26], Controlled PUF [48], Public PUF [16], Time Division Multiplexed PUF [49], Sense Amplifier Based PUF [50, 51], Current-Based PUF [52], Bistable Ring PUF [53], Sub-Threshold PUF [54], Power Distribution System PUF [55], and Cellular Nonlinear Networks PUF [56] are the other PUF types proposed in the literature. In this work, we focus on RO-PUFs, since they are the most convenient type for FPGA implementation and work more reliably under changing environmental conditions [10, 45].

# 3. DERIVATION OF QUALITY METRICS

Even though quite a number of different PUF structures and their analysis results are presented in the literature, robustness and uniqueness properties are generally not evaluated in detail. This prevents comparing PUF circuits using a fair and standard performance criterion and choosing the best fitting structure for a specific application. In this section, new quality metrics for uniqueness and robustness are derived and the confidence interval concept is adapted to ensure the trustworthiness of the results. In addition to these, two basic RO-PUF structures are implemented and their performance evaluation is presented according to the new set of quality metrics proposed.

#### 3.1. Derivation of Quality Metrics for Uniqueness

As explained briefly in Chapter 2, uniqueness is the inter-chip variation of PUFs. In the ideal case, PUF outputs generated on different ICs should be uniformly distributed and statistically independent. The most common metric for uniqueness,  $U_QM1$ , is the average HDs of outputs collected from different ICs. It has an ideal value of 0.5 and can be calculated as

$$U_{-}QM1 = \frac{2}{k(k-1)} \sum_{i=1}^{k-1} \sum_{j=i+1}^{k} \frac{HD(R_i, R_j)}{n}.$$

(3.1)

Even though the quality metric  $U_{-}QM1$  gives information about the performance of the system, it does not guarantee uniform distribution, since non-uniform outputs may have 50% HD. Due to this weakness of the  $U_{-}QM1$ , two PUF structures with different uniqueness performances may be evaluated as the same if  $U_{-}QM1$  is used as the only performance parameter.

At this point, we propose defining another quality metric to evaluate the unique-

ness of PUFs, depending on the fact that HDs of a uniformly distributed set of outputs will have a Gaussian distribution. This second quality metric,  $U_-QM2$ , should check how close to Gaussian the distribution of HDs is.  $U_-QM2$  can be calculated via correlating the HD distribution of PUF outputs with the ideal Gaussian distribution. A better quality design will exhibit higher correlation with the ideal Gaussian distribution in this sense.  $U_-QM2$  can be defined as

$$U_QM2 = Corr(DIS_HD, G(Mn(HD_PUF), \sigma)), \qquad (3.2)$$

where *Corr* is the correlation function, *G* is the function that generates data with the specified mean and standard deviation (STD) according to the Gaussian distribution,  $DIS\_HD$  is the HD distribution of the collected PUF outputs, and  $Mn(HD\_PUF)$  and  $\sigma$  are the mean and STD of HDs of the collected data, respectively. The closer the result is to 1, the closer the distribution is to Gaussian; hence, the circuit is better performing in terms of uniqueness.

In [18], Gilbert-Varshamov Bound (GVB) is utilized to determine the security of PUF outputs against exhaustive search attacks via calculating the minimum HD between two outputs within a set of outputs. In a similar manner, GVB can be used to determine the uniqueness of the structures as well. After collecting a certain number of outputs, the minimum distance, dHm, among them is determined in terms of bit count. Next, using dHm and PUF output length, N, R' is calculated as

$$R' \le 1 - H2(\underline{d}_{Hm}) = 1 + \underline{d}_{Hm}\log_2(\underline{d}_{Hm}) + (1 - \underline{d}_{Hm})log_2(1 - \underline{d}_{Hm}), \tag{3.3}$$

where  $\underline{d}_{Hm}$  is calculated as

$$\underline{d}_{Hm} = \frac{d_{Hm}}{N}.$$

(3.4)

Then, using the number of measurements, M, and PUF output length, N, the ideal R is calculated via

$$R = \frac{\log_2 M}{N}.\tag{3.5}$$

Proportion of R' to the ideal R can serve as a quality metric,  $U\_QM3$ , for uniqueness and can be calculated as

$$U_{-}QM3 = \frac{R}{R'}.$$

(3.6)

If the outputs are highly unique, minimum HD will be compatible with the GVB and  $U_QM3$  will converge to unity. Otherwise, the minimum HD will be worse than the bound states and  $U_QM3$  will be smaller than 1.

The main advantage of  $U_{-}QM3$  is its capability of comparing dissimilar sets of PUF outputs. For instance, a set of 1,000 outputs with 100 bit length can be compared with another set of 500 outputs with 128 bit length. The set with the higher  $U_{-}QM3$  value performs better than the other in terms of uniqueness.

In addition to these, GVB and  $U_QM3$  can be used to determine the number of circuits that can be identified with a previously determined security level and a certain length of PUF output. Similarly, the minimum required output length can be determined, for a previously set security level and the number of ICs to be identified. Here, the security level is  $\underline{d}_{Hm}$ , which is the ratio of the minimum HD between any two PUF outputs within a certain number of outputs to the output length and it is determined by the user.

For this purpose,  $U_{-}QM3$  is calculated, and a security level is set as  $\underline{d}_{Hm}$ . Then, R' is calculated again with the new  $\underline{d}_{Hm}$  and the result is multiplied by  $U_{-}QM3$  to determine R. Finally, using Equation 3.5, the designer can either set the number of PUF bits, N, and calculate the maximum number of circuits that can be identified, M, or set the number of circuits and calculate the minimum length of PUF output.

#### 3.2. Derivation of Quality Metrics for Robustness

Robustness is the intra-die variation that should be ideally zero for best performing PUF circuits, as discussed in Chapter 2. However, due to environmental variations and internal characteristics of PUF circuits, some bits of the output may flip within multiple measurements. The most common metric for robustness is  $R_QM1$ , which is the average HDs of measurements collected from a single IC and can be calculated as

$$R_{-}QM1 = \frac{1}{x} \sum_{y=1}^{x} \frac{HD(R_i, R'_{i,y})}{n}.$$

(3.7)

The ideal value of  $R_QM1$  is 0, which represents noise-free data.

Some of the application areas that utilize PUF circuits require 100% robust outputs. For this purpose, ECCs can be used to generate noise-free data at every measurement, even under changing environmental conditions.

Since the complexity and cost of ECC depend on the maximum number of erroneous bits they can recover,  $R_QM1$ , which is based on an average, does not give enough information for the design of such systems. Therefore, we propose using the maximum error rate within a certain number of measurements as the second quality metric,  $R_QM2$ , which can be calculated as

$$R_{-}QM2 = \max \frac{HD(R_i, R'_{i,y})}{n} \quad (1 \le y \le number \ of \ measurements). \tag{3.8}$$

The ideal value of  $R_QM2$  is 0, which indicates noise-free outputs. Higher values of  $R_QM2$  indicates the need of more and more complex ECC for the generation of 100% robust outputs.

Another set of data presented in [35] is the distribution of errors on the output bits. This data is used to mask the most erroneous bits and improve the robustness performances of PUF structures. This approach may be helpful in practice, if it is convenient to detect the most problematic bits in each circuit and eliminate them for future use. Thus, error reduction rate with masking a certain number of bits may serve as another quality metric,  $R_QM3$ , for robustness in PUF circuits. This can be calculated as

$$R_{-}QM3 = \frac{R_{-}QM1 - R'_{-}QM1}{R_{-}QM1},$$

(3.9)

where  $R'\_QM1$  represents the mean error rate after masking the most erroneous n bits. n can be selected depending on the robustness performance and cost requirements of the system. As n increases, the robustness performance of the structure increases. However, since more bits will be eliminated, area efficiency of the system will be degraded. A common method to improve the robustness of PUF circuits is majority voting (MV) [4,35]. Each bit of output is generated for a number of times and the result is determined via MV. This method increases the robustness performance of the structure especially under NOC. Thus, mean error rate after MV,  $R_-QM4$ , can serve as an important quality metric as well. This is calculated as

$$R_{-}QM4 = \frac{1}{x} \sum_{y=1}^{x} \frac{HD(R_i, R'_{MVi,y})}{n},$$

(3.10)

where the  $R'_{MVi,y}$  represents the output after MV for n times.

Stable bit count, the bits that generate the same output at each measurement, is also an important parameter. If stable bits are selected and used, the need for an error correction mechanism is eliminated. Therefore, stable bit count can serve as an another quality metric,  $R_-QM5$ , for robustness, which can be calculated as

$$R_{-}QM5 = \sum_{y=1}^{N} r_{y}$$

$$r_{y} = \begin{cases} 1, & R_{i,y} = R_{1,y}, \forall i \\ 0, & \text{otherwise} \end{cases},$$

$$(3.11)$$

where N is the number of bits in the output and  $R_{i,y}$  is the yth bit of the *i*th response.

Finally, since PUF outputs are very vulnerable to changes in the environment, PUF structures should be evaluated according to the metrics presented under both NOC and varying temperature and/or supply voltage for a proper performance evaluation.

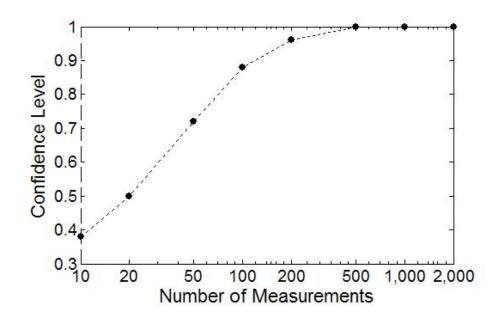

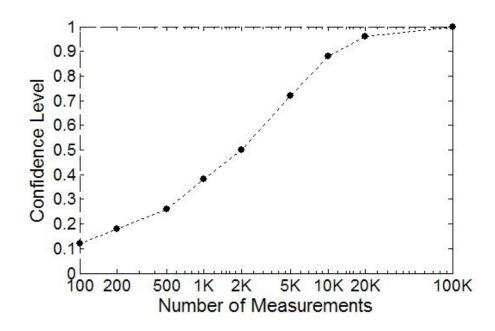

# 3.3. Confidence Interval and Confidence Level Concepts for PUF Evaluation

In the previous two sections, quality metrics that will be used to evaluate the uniqueness and robustness performance of PUF circuits are presented. However, the number of measurements to be taken for a reliable evaluation is still questionable. Therefore, in order to determine the trustworthiness of the results, confidence interval and confidence level concepts are adapted to PUF performance evaluation. Confidence interval is an estimation of values and indicates your measurements precision. Confidence level indicates the certainty of your estimation and expressed as a percentage. For instance, frequency of an RO can be expressed as 100 MHz with a confidence interval of 1 MHz and confidence level of 99%. This means that the frequency of the RO will be in the interval of 99-101 MHz with 99% certainty.

In this method, the number of measurements that has to be taken is determined according to the previously set confidence level and interval parameters, and using the STD of the outputs. This is calculated via the Chebyshev inequality as

$$Q(A) = 1 - 2\phi(\frac{c\sqrt{n}}{\sigma}), \qquad (3.12)$$

where c is the confidence interval, n is the number of measurements,  $\sigma$  is the STD of the outputs,  $\phi$  is the normal cumulative distribution function, and Q is the confidence level [57].

As the number of measurements increases, confidence level increases and/or confidence interval diminishes. For instance, 1,000 measurements can assure 99.9% confidence within 0.1% confidence interval, whereas 25 measurements can only provide 95% confidence level within 2% confidence interval when the STD of the HDs is 0.064, which is calculated based on the measurements taken from the FPGA environment.

Figure 3.1. Number of measurements - confidence level relation with confidence interval of 0.01 and STD of 0.064.

The relationship between the number of measurements, confidence interval, and confidence level is presented in Figures 3.1 and 3.2. As can be seen from the figures, confidence level of the results increases as the number of measurements increases. In addition to this, higher confidence level is assured with fewer measurements in Figure 3.1, since confidence interval is ten times larger than the one in Figure 3.2.

#### 3.4. Implementation of Two Basic RO-PUF Structures

Two RO-PUF structures presented in [48] are implemented on FPGA and their performances are evaluated according to the new set of quality metrics. Both designs employ a ring oscillator composed of five inverting stages and an enable input as illustrated in Figure 2.16. To maintain equal wire loads and minimize the systematic variation, the RO is built as a hard macro. One bit of PUF output is generated by comparing the oscillation frequencies of two ROs. Frequency comparison is done via using two counters, which count the number of oscillations of the two ROs within a certain time interval. In the first structure, n + 1 ROs are implemented and each two ROs that are placed next to each other are compared to generate one bit output. This structure generates n bit outputs using n + 1 ROs. In the second structure, 2n ROs

Figure 3.2. Number of measurements - confidence level relation with confidence interval of 0.001 and STD of 0.064.

are used to generate n bit outputs. In this structure, each RO is used only once and adjent ROs are used to generate the output bits, similar to the first structure.

#### 3.5. Analysis of Experimental Data